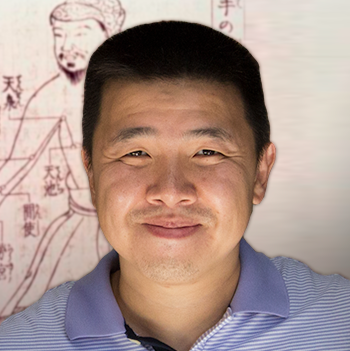

Chi Kin Chan

age ~55

from Houston, TX

- Also known as:

-

- Chi K Chan

- Florio C Chan

- Florio K Chan

- Chan Florio

Chi Chan Phones & Addresses

- Houston, TX

- San Francisco, CA

- Daly City, CA

- Oakland, CA

Lawyers & Attorneys

Chi Chan - Lawyer

view sourceOffice:

Pang & Associates

Specialties:

Civil Litigation

Criminal Litigation

Criminal Litigation

ISLN:

919757668

Admitted:

2000

License Records

Chi Heem Chan

Address:

1369 16 Ave, San Francisco, CA 94122

License #:

33284 - Expired

Issued Date:

Jun 8, 1998

Renew Date:

Jun 8, 1998

Expiration Date:

Jan 25, 1999

Type:

Engineer Intern

Chi Heem Chan

Address:

1369 16 Ave, San Francisco, CA 94122

License #:

25397 - Expired

Issued Date:

Aug 28, 1998

Renew Date:

Mar 1, 2009

Expiration Date:

Sep 30, 2011

Type:

Master Electrician

Chi Heem Chan

Address:

1369 16 Ave, San Francisco, CA 94122

License #:

33284 - Expired

Issued Date:

Jan 25, 1999

Renew Date:

Feb 1, 2009

Expiration Date:

Jan 31, 2011

Type:

Professional Engineer

Medicine Doctors

Chi Yuen Chan

view sourceResumes

Chi Chan Stafford, TX

view sourceWork:

JC, Inc

Feb 2013 to 2000 WL Marketing, Inc

Houston, TX

May 2009 to Dec 2012 Applied Optoelectronics, Inc

Sugar Land, TX

Mar 2006 to Feb 2009

Receiving Administrator

Feb 2013 to 2000 WL Marketing, Inc

Houston, TX

May 2009 to Dec 2012 Applied Optoelectronics, Inc

Sugar Land, TX

Mar 2006 to Feb 2009

Receiving Administrator

Education:

University of Houston

2002 to 2005

Bachelor's in Accounting Houston Community College

2000 to 2002 Alief Elsik High School

1996 to 2000

High School Diploma

2002 to 2005

Bachelor's in Accounting Houston Community College

2000 to 2002 Alief Elsik High School

1996 to 2000

High School Diploma

Chi Fay Chan Santiago Bayamn, PR

view sourceWork:

Medtronic

Oct 2011 to Present

Data Specialist Univeristy of Puerto Rico, Mayaguez Campus

Mayagez, PR

Aug 2010 to Dec 2010

Research - Drying Curve Model Revision University of Puerto Rico, Mayaguez Campus

Mayagez, PR

Aug 2010 to Dec 2010

Chemical Engineering Process Design I & II Course Projects Bristol-Myers Squibb

Humacao, Puerto Rico, US

Jun 2010 to Aug 2010

Summer Internship SunCom Wireless, Mega Cellular

Bayamn, PR

Jun 2005 to Jul 2005

Customer Service Government of Puerto Rico, Department of Family

Bayamn, PR

Jun 2004 to Jul 2004

Office Assistant Government of Puerto Rico, Department of Property Registration

Bayamn, PR

Jun 2003 to Jul 2003

Office Assistant

Oct 2011 to Present

Data Specialist Univeristy of Puerto Rico, Mayaguez Campus

Mayagez, PR

Aug 2010 to Dec 2010

Research - Drying Curve Model Revision University of Puerto Rico, Mayaguez Campus

Mayagez, PR

Aug 2010 to Dec 2010

Chemical Engineering Process Design I & II Course Projects Bristol-Myers Squibb

Humacao, Puerto Rico, US

Jun 2010 to Aug 2010

Summer Internship SunCom Wireless, Mega Cellular

Bayamn, PR

Jun 2005 to Jul 2005

Customer Service Government of Puerto Rico, Department of Family

Bayamn, PR

Jun 2004 to Jul 2004

Office Assistant Government of Puerto Rico, Department of Property Registration

Bayamn, PR

Jun 2003 to Jul 2003

Office Assistant

Education:

University of Puerto Rico, Mayaguez Campus

Mayagez, PR

Jan 2004 to Jan 2010

BS in Chemical Engineering

Mayagez, PR

Jan 2004 to Jan 2010

BS in Chemical Engineering

Chi Chan Houston, TX

view sourceWork:

University of Houston

Houston, TX

Apr 2010 to May 2010

Career affair volunteer at UH campus Houston Children's Hospital

Houston, TX

2008 to 2008

Volunteer Greeter, cleaner and cooker Kim's electrical company

Hong Kong, Hong Kong Island

Nov 2006 to 2007

Assistant Manager

Houston, TX

Apr 2010 to May 2010

Career affair volunteer at UH campus Houston Children's Hospital

Houston, TX

2008 to 2008

Volunteer Greeter, cleaner and cooker Kim's electrical company

Hong Kong, Hong Kong Island

Nov 2006 to 2007

Assistant Manager

Education:

University of Houston, C.T. Bauer College of Business

Houston, TX

May 2012

Bachelor of Business Administration in Marketing

Houston, TX

May 2012

Bachelor of Business Administration in Marketing

Name / Title

Company / Classification

Phones & Addresses

President

JTJ PRODUCTION INC

1077 Powell St, San Francisco, CA 94108

Owner

Chin Tao Chinese Restaurant

Eating Place

Eating Place

13251 Jones Rd, Houston, TX 77070

(281)4690103

(281)4690103

Director

6800 SW FREEWAY, INC

Nonclassifiable Establishments

Nonclassifiable Establishments

6606 Marinette Dr, Houston, TX 77036

6800 Marinette Dr, Houston, TX 77036

3234 Meadway Dr, Houston, TX 77082

6800 Marinette Dr, Houston, TX 77036

3234 Meadway Dr, Houston, TX 77082

Principal

Kowloon Cafe

Eating Place

Eating Place

32757 S Belami Loop, Union City, CA 94587

15828 Hesperian Blvd, San Lorenzo, CA 94580

(510)2766888

15828 Hesperian Blvd, San Lorenzo, CA 94580

(510)2766888

President

MANSON INC

5184 Sonoma Blvd STE 340, Vallejo, CA 94589

President

GREAT TREND GARMENT INC

325 9 St 3/F, San Francisco, CA 94103

325 9 St, San Francisco, CA 94103

325 9 St, San Francisco, CA 94103

President, Director

CHUNG TIN CORPORATION

9918 Inwood Shadows Chi Shung Chan, Houston, TX 77091

6305 Antoine Dr A-1, Houston, TX 77091

6305 Antoine Dr A-1, Houston, TX 77091

Principal

Origami Empire

Business Services at Non-Commercial Site · Nonclassifiable Establishments

Business Services at Non-Commercial Site · Nonclassifiable Establishments

340 Eddy St, San Francisco, CA 94102

Us Patents

-

Dual-Bus System For Communicating With A Processor

view source -

US Patent:8041855, Oct 18, 2011

-

Filed:Jan 27, 2009

-

Appl. No.:12/360764

-

Inventors:Jingzhao Ou - Sunnyvale CA, US

Chi Bun Chan - San Jose CA, US -

Assignee:Xilinx, Inc. - San Jose CA

-

International Classification:G06F 3/00

G06F 13/28

G06F 13/00

G06F 13/36 -

US Classification:710 35, 710 14, 710 27, 710308

-

Abstract:A system for communicating with a processor within an integrated circuit can include a dual-bus adapter () coupled to the processor () through a first communication channel () and a second communication channel (). The dual-bus adapter further can be coupled to a memory map interface () through which at least one peripheral device communicates with the processor. Single word operations can be exchanged between the processor and the dual-bus adapter through the first communication channel. Burst transfer operations can be performed by exchanging signaling information between the processor and the dual-bus adapter over the first communication channel and exchanging data words between the processor and the dual-bus adapter through the second communication channel.

-

Power Estimation In High-Level Modeling Systems

view source -

US Patent:8082530, Dec 20, 2011

-

Filed:Feb 20, 2009

-

Appl. No.:12/389468

-

Inventors:Jingzhao Ou - Sunnyvale CA, US

Chi Bun Chan - San Jose CA, US -

Assignee:Xilinx, Inc. - San Jose CA

-

International Classification:G06F 9/455

-

US Classification:716109, 716106

-

Abstract:A computer-implemented method of estimating power usage for high-level blocks of a high-level modeling system (HLMS) circuit design can include generating a low-level circuit design from the HLMS circuit design. The method can include simulating the low-level circuit design and storing power usage data, from the simulating, for each of a plurality of circuit elements of the low-level circuit design. The circuit elements can be correlated with the high-level blocks of the HLMS circuit design. A power query of a selected block of the HLMS circuit design can be received and a measure of power usage for the selected high-level block can be determined according to the power usage data for selected ones of the plurality of circuit elements correlated with the selected high-level block. The measure of power usage for the selected high-level block can be output.

-

Method And Apparatus For Profiling A Hardware/Software Embedded System

view source -

US Patent:8145467, Mar 27, 2012

-

Filed:Feb 25, 2008

-

Appl. No.:12/036920

-

Inventors:Jingzhao Ou - Sunnyvale CA, US

Chi Bun Chan - San Jose CA, US -

Assignee:Xilinx, Inc. - San Jose CA

-

International Classification:G06F 17/50

-

US Classification:703 15

-

Abstract:Method and apparatus for profiling a hardware/software embedded system are described. In one example, a hardware co-simulation interface is generated between a programmable logic device (PLD) configured with the embedded system and a computer based on a plurality of events. The embedded system in the PLD is simulated. During the simulation of the embedded system, occurrence of at least one event is detected to produce profiling data. The profiling data is stored into shared first-in-first-out (FIFO) logic of the PLD and the computer. The profiling data is retrieved from the shared FIFO logic at the computer.

-

Method And Apparatus For Modeling Processor-Based Circuit Models

view source -

US Patent:8229725, Jul 24, 2012

-

Filed:Sep 29, 2008

-

Appl. No.:12/240874

-

Inventors:Jingzhao Ou - Sunnyvale CA, US

Chi Bun Chan - San Jose CA, US

Shay Ping Seng - San Jose CA, US -

Assignee:Xilinx, Inc. - San Jose CA

-

International Classification:G06F 17/50

G06F 9/455 -

US Classification:703 15, 703 25

-

Abstract:Method and apparatus for modeling processor-based circuit models are described. Some examples relate to designing a circuit model having a processor system and custom logic. A bus adapter coupled to a bus of the processor system is generated. A shared memory interface between the custom logic and the bus adapter is generated. The shared memory interface includes a memory map for the processor system. A clock wrapper having a first clock input and a second clock input is generated. The first clock input drives the custom logic and first shared memory of the shared memory interface. The second clock input drives the processor system.

-

Simulation And Emulation Of A Circuit Design

view source -

US Patent:8265918, Sep 11, 2012

-

Filed:Oct 15, 2009

-

Appl. No.:12/579846

-

Inventors:Hem C. Neema - Sunnyvale CA, US

Chi Bun Chan - San Jose CA, US

Kumar Deepak - San Jose CA, US

Nabeel Shirazi - Saratoga CA, US -

Assignee:Xilinx, Inc. - San Jose CA

-

International Classification:G06F 17/50

-

US Classification:703 14, 703 13

-

Abstract:Co-simulation platforms generally include a software-based system and a hardware-based system in which different portions of the circuit design are either simulated in a software-based system or emulated on a hardware-based system. Before a model of circuit design can be co-simulated, the circuit design must be transformed and configured into a form that can execute and interface with a specific hardware-based system. The embodiments of the present invention provide a method, system, and article of manufacture for co-simulation of a portion of a circuit design and achieve an advance in the art by improving co-simulation configuration and setup and providing co-simulation adjustment capabilities during runtime.

-

Method And Circuit For Secure Definition And Integration Of Cores

view source -

US Patent:8417965, Apr 9, 2013

-

Filed:Apr 7, 2010

-

Appl. No.:12/755760

-

Inventors:Arvind Sundararajan - Sunnyvale CA, US

Chi Bun Chan - San Jose CA, US

Nabeel Shirazi - Saratoga CA, US -

Assignee:Xilinx, Inc. - San Jose CA

-

International Classification:G06F 11/30

G06F 12/14

G06F 7/04

G06F 17/30

G06F 9/445

H04L 29/06

H04L 9/00

H04L 9/30

H04K 1/00

H04N 7/16 -

US Classification:713189, 713150, 713187, 380 30, 726 26, 717174

-

Abstract:An embodiment of the present invention provides a method and circuit for secure definition and integration of a core into a circuit design without exposing the core. In one embodiment, a core development package is obtained. The core development package includes an encrypted core and a decryption key of the encrypted core. The decryption key is encrypted with an asymmetric cipher. The encrypted core is transmitted from the design tool to a trusted platform module. The decryption key is decrypted with a private key of the asymmetric cipher. The encrypted core is decrypted within the trusted platform module. One or more design tool operations are performed using the decrypted core.

-

Linking Untimed Data-Path And Timed Control-Path Models

view source -

US Patent:8650019, Feb 11, 2014

-

Filed:Jan 28, 2010

-

Appl. No.:12/695800

-

Inventors:Arvind Sundararajan - Sunnyvale CA, US

Chi Bun Chan - San Jose CA, US -

Assignee:Xilinx, Inc. - San Jose CA

-

International Classification:G06F 17/50

-

US Classification:703 14, 703 13

-

Abstract:Approaches for creating a timed hybrid simulation model for a circuit design specification. An untimed, high-level language (HLL) data-path model is input, along with an HLL data-path interface specification that specifies input ports of the HLL data-path model. A hardware description language (HDL) control-path model that specifies port attributes and associated stitching directives is generated. Each stitching directive specifies a control port and an associated one of the input ports of the HLL data-path model. The HLL data-path and HDL control-path models are linked () to create the timed hybrid simulation model, and the timed hybrid simulation model is stored in a processor-readable storage medium.

-

Automatically Documenting Circuit Designs

view source -

US Patent:8650517, Feb 11, 2014

-

Filed:Oct 19, 2009

-

Appl. No.:12/581631

-

Inventors:Arvind Sundararajan - Sunnyvale CA, US

Nabeel Shirazi - Saratoga CA, US

Jingzhao Ou - San Jose CA, US

Chi Bun Chan - San Jose CA, US -

Assignee:Xilinx, Inc. - San Jose CA

-

International Classification:G06F 17/50

-

US Classification:716104, 716101, 716139

-

Abstract:Within a system comprising a processor and a memory, a method of automatically documenting a circuit design can include determining an assignment of a user comment entity (UCE) of a high level modeling system (HLMS) circuit design to an HLMS block of the HLMS circuit design, translating each HLMS block of the HLMS circuit design into a hardware description language (HDL) representation of the HLMS block, and for each HLMS block assigned a UCE, inserting within the HDL representation, by the processor, content of the UCE that is assigned to the HLMS block in the form of a comment. The HDL representations can be stored within the memory.

Vehicle Records

-

Chi Chan

view source -

Address:12423 Leader St, Houston, TX 77072

-

VIN:JN1BZ36A57M650173

-

Make:NISSAN

-

Model:350Z

-

Year:2007

Wikipedia References

Chi Ming Chan

Plaxo

chi ying chan

view sourcedop at cyc workshop

chi fai chan

view source

Chi Chan

view sourceSales at Courtesy Chevrolet

Myspace

Flickr

Chi Keung Chan

view source

Chi Chan

view source

Chi Chan Mak

view source

Chi Chung Chan

view source

Chi Keung Chan

view source

Mc Dha Chi Chan

view source

Chi Chan Nghi

view source

Shar Wing Chi Chan

view sourceClassmates

Chi Ho Chan

view sourceSchools:

Oak Grove Lutheran High School Fargo ND 1989-1993

Community:

Bodil Ehlbeck, Mary Anderson

Chi Ming Chan

view sourceSchools:

Berendo Junior High School Los Angeles CA 1975-1977

Chi Wai Chan

view sourceSchools:

University of Houston - Main Campus Houston TX 1974-1978

Community:

Geoffrey Jones, Daniel Varney

Chi Hin Chan

view sourceSchools:

Fraser High School Mississauga Morocco 1998-2002

Community:

Peter Macmillan, Phyllis Walker, Scott Macneil

Chi Chan

view sourceSchools:

Homecrest Public School 153 Brooklyn NY 1980-1986

Community:

John Russo, Frank Troise, Ralph Mendez

Chi Fai Chan

view sourceSchools:

Linwood Middle School North Brunswick NJ 2004-2008

Community:

Sefrah Easie, Marquise Ridriguez

Hsin-Chi Chan, Flagstaff ...

view sourceGoogleplus

Chi Chan

Work:

銀石[GINSHI]

Chi Chan

Chi Chan

Tagline:

Ipinaglalaban ko ang Wikang Filipino at karapatan ng mga Isda

Bragging Rights:

Maganda ako mag-sulat!!!!

Chi Chan (陳志平)

Chi Chan

Chi Chan

Chi Chan

Tagline:

I collect antique horseshoes and limited-edition toilet paper. Contact me if you have interest in the same.

Chi Chan

Youtube

Get Report for Chi Kin Chan from Houston, TX, age ~55

![Chi-chan's Moogle Song [Ichigo Mashimaro MAD] Chi-chan's Moogle Song [Ichigo Mashimaro MAD]](https://i.ytimg.com/vi/yk14CmgaunY/0.jpg)