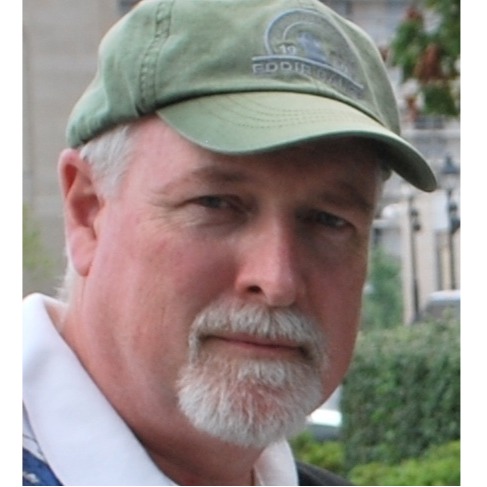

Mark A Mcclain

age ~70

from San Diego, CA

- Also known as:

-

- Mark Linda Mcclain

- Mark A Clain

- Mark Mc Clain

- Linda Mcclain

- Phone and address:

-

12598 Dormouse Rd, San Diego, CA 92129

(858)6030552

Mark Mcclain Phones & Addresses

- 12598 Dormouse Rd, San Diego, CA 92129 • (858)6030552 • (858)5382300 • (858)5382454

- Harrison, MI

- 12598 Dormouse Rd, San Diego, CA 92129 • (858)6030452

Emails

Medicine Doctors

Mark A. Mcclain

view sourceSpecialties:

Anesthesiology

Work:

Old Pueblo Anesthesia

5301 E Grant Rd, Tucson, AZ 85712

(520)3242200 (phone), (520)4456019 (fax)

5301 E Grant Rd, Tucson, AZ 85712

(520)3242200 (phone), (520)4456019 (fax)

Education:

Medical School

Tufts University School of Medicine

Graduated: 2007

Tufts University School of Medicine

Graduated: 2007

Languages:

English

Spanish

Spanish

Description:

Dr. McClain graduated from the Tufts University School of Medicine in 2007. He works in Tucson, AZ and specializes in Anesthesiology. Dr. McClain is affiliated with Tucson Medical Center.

Mark A. Mcclain

view sourceSpecialties:

Psychologist

Work:

Behavioral Associates

1 Poston Rd STE 145, Charleston, SC 29407

(843)5564157 (phone), (843)7638747 (fax)

1 Poston Rd STE 145, Charleston, SC 29407

(843)5564157 (phone), (843)7638747 (fax)

Languages:

English

Description:

Dr. Mcclain works in Charleston, SC and specializes in Psychologist.

Mark McClain

view sourceName / Title

Company / Classification

Phones & Addresses

BEN NET INC

HEALING HANDS ALLIANCE, INC

EAST CLEVELAND WARD 2 COALITION INCORPORATED

GENESIS CHILD DEVELOPMENT CENTER

NOPHIA DEVELOPMENT CORPORATION

Us Patents

-

Computer System Initialization With Boot Program Stored In Sequential Access Memory, Controlled By A Boot Loader To Control And Execute The Boot Program

view source -

US Patent:6601167, Jul 29, 2003

-

Filed:Jan 14, 2000

-

Appl. No.:09/483318

-

Inventors:Ralph E. Gibson - Campbell CA

Loren J. Shalinsky - Mountain View CA

Mark A. McClain - San Diego CA -

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G06F 9445

-

US Classification:713 2, 713 1

-

Abstract:A computer system includes a processor and a sequential access memory having a boot program stored therein. A boot loader includes a state machine which, in response to initialization of the computer system, controls the sequential access memory to read the boot program and then controls the processor to jump to the boot program in the sequential access memory. The first memory page of the boot program causes further boot code to be transferred to a Random Access Memory (RAM). The processor then jumps to the code in the RAM, which causes the remainder of the boot code to be transferred from the sequential access memory to the RAM and executed.

-

Password And Dynamic Protection Of Flash Memory Data

view source -

US Patent:6731536, May 4, 2004

-

Filed:Mar 7, 2002

-

Appl. No.:10/091767

-

Inventors:Mark Alan McClain - San Diego CA

Michael Garrett Tanaka - San Jose CA

Ralf Muenster - Los Altos CA -

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G11C 700

-

US Classification:36518504, 36518529, 36518901, 365218

-

Abstract:In protecting Flash memory data, a flexible system and method provides for different levels of protection. It offers the ability to dynamically lock a sector of memory using a dynamic protection bit in volatile memory. It offers persistent locking of a sector using a non-volatile bit in memory and locking this status using a lock bit in volatile memory. It offers yet further protection by including a password mode which requires a password to clear the lock bit. The password is located in an unreadable, one time programmable area of the memory. The memory also includes areas, whose protection state is controlled by an input signal, for storing boot code in a protected manner.

-

Computer System Initialization Via Boot Code Stored In A Non-Volatile Memory Having An Interface Compatible With Synchronous Dynamic Random Access Memory

view source -

US Patent:7058779, Jun 6, 2006

-

Filed:Mar 5, 2002

-

Appl. No.:10/091766

-

Inventors:Mark Alan McClain - San Diego CA, US

-

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G06F 12/00

-

US Classification:711170, 711100, 711104, 711105, 711111, 711112, 711169, 713 1, 713 2, 710 10

-

Abstract:A method for reducing the number of interface lines and non-volatile memory devices in a computer system includes providing a non-volatile memory having a SDRAM style interface. A system having both non-volatile memory and SDRAM has reduced interface lines by providing only one memory interface. A system where the SDRAM interface logic is initialized by code stored in the non-volatile memory having a SDRAM style interface, eliminating any requirement for other non-volatile memory, independent of the SDRAM interface, from which to initialize the system.

-

Memory Erase Management System

view source -

US Patent:7443712, Oct 28, 2008

-

Filed:Sep 7, 2006

-

Appl. No.:11/470958

-

Inventors:Colin Bill - Cupertino CA, US

Mark McClain - San Diego CA, US

Michael VanBuskirk - Saratoga CA, US -

Assignee:Spansion LLC - Sunnyvale CA

-

International Classification:G11C 11/00

-

US Classification:365148, 365163, 365204

-

Abstract:A memory erase management system is provided, including providing a resistive change memory cell, coupling a first line to the resistive change memory cell, coupling a line buffer to the first line, providing a charge storage device coupled to the line buffer, and performing a single pulse erase of the resistive change memory cell by discharging a current from the charge storage device through the resistive change memory cell.

-

Optical Erase Memory Structure

view source -

US Patent:7781806, Aug 24, 2010

-

Filed:Apr 18, 2008

-

Appl. No.:12/106180

-

Inventors:Michael VanBuskirk - Saratoga CA, US

Mark McClain - San Diego CA, US -

Assignee:Spansion LLC - Sunnyvale CA

-

International Classification:H01L 27/148

-

US Classification:257225, 257 98, 257324, 257462, 257E27127, 438 24, 438 29

-

Abstract:A method for providing an optical erase memory structure including: forming a metal-insulator-metal memory cell; positioning a light emitting diode adjacent to the metal-insulator-metal memory cell; and emitting a light emission from the light emitting diode for erasing the metal-insulator-metal memory cell.

-

System And Method For Improved Memory Performance In A Mobile Device

view source -

US Patent:20060095622, May 4, 2006

-

Filed:Oct 28, 2004

-

Appl. No.:10/975629

-

Inventors:Stephan Rosner - Campbell CA, US

Mark McClain - San Diego CA, US

Eugen Gershon - San Jose CA, US -

International Classification:G06F 13/00

-

US Classification:710107000

-

Abstract:A system and method are disclosed for improved memory performance in a mobile device. A mobile device incorporating teachings disclosed herein may include, for example, a central processing unit (CPU) residing on a first chip. The mobile device may also include a memory system residing on a second chip. The memory system may include, for example, a memory controller and at least one type of memory combined in a single multi-chip package. The multi-chip package may effectively internalize higher pin count interfaces interconnecting the memory controller and the at least one type of memory. With some implementations, a high frequency, low pin-count external bus may form at least a portion of a link communicatively coupling the multi-chip package and the CPU. In practice, the high frequency, low pin-count external bus may physically connect to a bus interface residing on the first chip. The bus interface may be communicatively coupled to the CPU via an internal CPU bus also located on the first chip. In operation, the bus interface may provide bus translation between the high frequency, low pin-count external bus, and the internal CPU bus.

-

Memory Device With Internal Combination Logic

view source -

US Patent:20160307611, Oct 20, 2016

-

Filed:Feb 24, 2016

-

Appl. No.:15/052709

-

Inventors:- San Jose CA, US

Mark Alan McClain - San Diego CA, US -

International Classification:G11C 8/00

-

Abstract:Embodiments of the present invention include an apparatus, method, and system for integrating data processing logic with memory. An embodiment of a memory integrated circuit is designed to execute a task on the data in a memory array within a memory integrated circuit. The memory integrated circuit can include a memory array, a data access component, a data holding component, and a logic component. The data access component can be coupled to the memory array and configured to provide an address to the memory array. The data holding component can be coupled to the memory array and configured to temporarily store the data in the memory array located at the address. The logic component can be coupled to both the data access component and the data holding component, and be configured to execute a task using data received from the data holding component. The logic component can include combinational or sequential logic.

-

Memory Device With Internal Combination Logic

view source -

US Patent:20140177375, Jun 26, 2014

-

Filed:Dec 21, 2012

-

Appl. No.:13/725415

-

Inventors:- Sunnyvale CA, US

Mark A. McClain - San Diego CA, US -

Assignee:Spansion LLC - Sunnyvale CA

-

International Classification:G11C 8/00

-

US Classification:36523001

-

Abstract:Embodiments of the present invention include an apparatus, method, and system for integrating data processing logic with memory. An embodiment of a memory integrated circuit is designed to execute a task on the data in a memory array within a memory integrated circuit. The memory integrated circuit can include a memory array, a data access component, a data holding component, and a logic component. The data access component can be coupled to the memory array and configured to provide an address to the memory array. The data holding component can be coupled to the memory array and configured to temporarily store the data in the memory array located at the address. The logic component can be coupled to both the data access component and the data holding component, and be configured to execute a task using data received from the data holding component. The logic component can include combinational or sequential logic.

Resumes

Senior Regulatory Operations Officer

view sourcePosition:

Senior Pharmacist at United States Public Health Service

Location:

Deep River, Connecticut

Industry:

Pharmaceuticals

Work:

United States Public Health Service since Dec 2002

Senior Pharmacist

FDA 2002 - 2011

CSO

U.S. Coast Guard May 1998 - Nov 2002

Chief Pharmacist, USCG Academy Pharmacy

Senior Pharmacist

FDA 2002 - 2011

CSO

U.S. Coast Guard May 1998 - Nov 2002

Chief Pharmacist, USCG Academy Pharmacy

Education:

The University of New Mexico 1988 - 1991

BSPharm, Pharmacy

BSPharm, Pharmacy

Interests:

Tennis, underwater hockey, mountain biking, spear fishing, SCUBA diving, boating, surfing, hunting (bow & shotgun), kayaking, choral singing, and foreign travel

Accounting Manager At Pentaflex

view sourcePosition:

Accounting Manager at Pentaflex

Location:

Springfield, Ohio

Industry:

Automotive

Work:

Pentaflex since Apr 1996

Accounting Manager

Harding Machine Oct 1981 - Mar 1996

Controller

Accounting Manager

Harding Machine Oct 1981 - Mar 1996

Controller

Education:

The Ohio State University 1977 - 1981

BS, Accounting

BS, Accounting

Interests:

Home remodeling, softball, and golf. Avid OSU Buckeye Fan and loyal Dallas Cowboy Fan

Certifications:

Practical Auditing and Recognition of Quality Management, Alan Griffin Associates UK LTD IQA International Register of Certifed Auditors

Lean for the WorkPlace, Strategic Leadership Solutions

Lean for the WorkPlace, Strategic Leadership Solutions

Mark Mcclain

view sourceLocation:

United States

Mark Mcclain

view sourceLocation:

United States

Teacher/Coach In Colleton County School District

view sourcePosition:

Teacher/Coach at Marion County School District

Location:

Florence, South Carolina

Industry:

Sports

Work:

Marion County School District - Creek Bridge High School since Jun 2012

Teacher/Coach

Florence School District #1 Jun 2005 - May 2012

Teacher/Coach

Fairfield School District Jun 2003 - Jun 2005

Teacher/Coach

Teacher/Coach

Florence School District #1 Jun 2005 - May 2012

Teacher/Coach

Fairfield School District Jun 2003 - Jun 2005

Teacher/Coach

Education:

South Carolina State University 1988 - 1992

Bachelor of Science (BS), Physical Education Teaching and Coaching Wilson High School 1983 - 1987

Diploma, High School/Secondary Diploma Programs

Bachelor of Science (BS), Physical Education Teaching and Coaching Wilson High School 1983 - 1987

Diploma, High School/Secondary Diploma Programs

Fellow At Spansion Inc.

view sourcePosition:

Fellow at Spansion Inc.

Location:

Greater San Diego Area

Industry:

Semiconductors

Work:

Spansion Inc. since Jul 2004

Fellow

Fellow

Skills:

Semiconductors

ASIC

Microprocessors

IC

Product Marketing

Semiconductor Industry

Flash Memory

Network Architecture

Programmable Logic

RISC

ASIC

Microprocessors

IC

Product Marketing

Semiconductor Industry

Flash Memory

Network Architecture

Programmable Logic

RISC

Youtube

Myspace

mark mcclain

view sourcePlaxo

Mark McClain

view sourceHVAC Tech at Letsos Co.

Mark McClain

view sourceMusic Teacher (Kindergarten - Grade 3) at Giddings...

Flickr

Mark McClain

view source

Mark McClain

view source

Mark McClain

view source

Mark McClain

view source

Mark McClain

view source

Mark A McClain

view source

Mark Mcclain Sr.

view source

Mark McClain

view sourceGoogleplus

Mark Mcclain

Work:

Parkland College - Technical Support Specialist (2001)

Education:

Parkland College - Computer Sci

Mark Mcclain

Lived:

Redmond, WA

Findlay, OH

San Diego, CA

Findlay, OH

San Diego, CA

Bragging Rights:

Drove a BlueBird bus at 90+ mph. (It had lights and a siren!!)

Mark Mcclain

Mark Mcclain

Mark Mcclain

Mark Mcclain

Mark Mcclain

Mark Mcclain

Classmates

Mark McClain

view sourceSchools:

McCutcheon High School Lafayette IN 1971-1975, Carmel High School Carmel IN 1972-1975

Community:

Joseph Boeckman, Jamie Bodkin

Mark McClain

view sourceSchools:

North Hall High School Gainesville GA 1985-1989

Community:

Rita Prenavo

Mark McClain

view sourceSchools:

Heritage High School Conyers GA 1984-1988

Mark McClain

view sourceSchools:

Washington Elementary School Lynwood CA 1966-1971, Boulter Middle School Tyler TX 1972-1972

Mark McClain

view sourceSchools:

North Oldham High School Goshen KY 2001-2005

Community:

Joel Nivens, Amber Attig, Allison Oetinger

Mark McClain

view sourceSchools:

Fayette Academy Somerville TN 1987-1991

Mark McClain

view sourceSchools:

Bourbon County High School Paris KY 1969-1973

Community:

Eric Gnau

Mark McClain

view sourceSchools:

Sacred Heart of Jesus & Mary School Southampton NY 1959-1963, Mercy High School Riverhead NY 1963-1967

Community:

James Ewers, Jim Brown

Get Report for Mark A Mcclain from San Diego, CA, age ~70