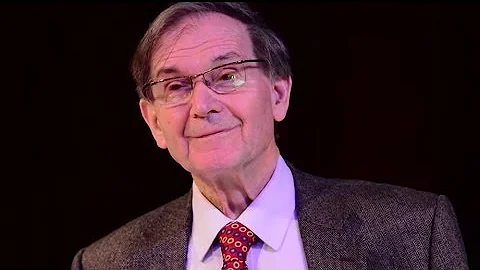

Edward C Prosser

age ~63

from Rochester, MN

- Also known as:

-

- Edward S Prosser

- Ed C Prosser

- Phone and address:

-

1506 Buck Ridge Dr NE, Rochester, MN 55906

(507)2520353

Edward Prosser Phones & Addresses

- 1506 Buck Ridge Dr NE, Rochester, MN 55906 • (507)2520353

- Madison, WI

- Bloomington, IN

- Menlo Park, CA

- Saint Paul, MN

- Saint Louis Park, MN

License Records

Edward J Prosser

License #:

36BI00572800 - Expired

Category:

Master Plumbers

Issued Date:

Jan 5, 1978

Type:

Master Plumber

Edward J Prosser

License #:

36BI00572800 - Expired

Category:

Master Plumbers

Issued Date:

Jan 5, 1978

Type:

Master Plumber

Edward J Prosser

License #:

36BI00572800 - Expired

Category:

Master Plumbers

Issued Date:

Jan 5, 1978

Type:

Master Plumber

Edward J Prosser

License #:

36BI00572800 - Expired

Category:

Master Plumbers

Issued Date:

Jan 5, 1978

Type:

Master Plumber

Us Patents

-

Object-Oriented Compiler Mechanism For Automatically Selecting Among Multiple Implementations Of Objects

view source -

US Patent:6360360, Mar 19, 2002

-

Filed:Feb 8, 1996

-

Appl. No.:08/598360

-

Inventors:Cary Lee Bates - Rochester MN

Edward Curtis Prosser - Rochester MN

William Jon Schmidt - Rochester MN -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 945

-

US Classification:717 9

-

Abstract:In an object-oriented or object-based computer system, a compiler mechanism allows a compiler to automatically select among multiple implementations of an object to optimize the performance of the compiled code. The selection may be made by assigning a weighted cost to each of the implementations, and selecting the implementation with the lowest weighted cost, where the weighted cost represents estimates of execution frequencies for each of the objects functions. In the alternative, for implementations that have different interfaces, the selection may be made based on an evaluation of the functions used in the program compared to the functions provided by the different implementations, and selecting an implementation that contains all functions issued against the object with a minimum of functions that are not issued against the object.

-

Method And Apparatus For Allocating Registers During Code Compilation Using Different Spill Strategies To Evaluate Spill Cost

view source -

US Patent:6523173, Feb 18, 2003

-

Filed:Jan 11, 2000

-

Appl. No.:09/480978

-

Inventors:Peter Edward Bergner - Apple Valley MN

Edward Curtis Prosser - Rochester MN -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 945

-

US Classification:717152, 717158

-

Abstract:Register allocation during computer program code compilation is accomplished by determining a set of spill candidates, by evaluating a cost function for each spill candidate using a plurality of spill strategies, and by selecting the spill candidate having the lowest cost function value. Preferably, the set of possible spill candidates is determined by the Chaitin method of constructing an interference graph of all live ranges of symbolic registers, and iteratively removing nodes and placing them on a stack. Preferably, multiple spill strategies are represented as varying numbers of deaths N of live ranges of other symbolic registers, a spill strategy N signifying that spill code is introduced whenever the number of deaths occurring between two successive uses of a symbolic register equals or exceeds N. In the preferred embodiment, the cost is a function of the number, type and frequency of each operation introduced by the spill, and is divided by a benefit factor represented as the degree of the node.

-

Incorporating Register Pressure Into An Inlining Compiler

view source -

US Patent:6983459, Jan 3, 2006

-

Filed:Apr 6, 1999

-

Appl. No.:09/286862

-

Inventors:Edward Curtis Prosser - Rochester MN, US

William Jon Schmidt - Rochester MN, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 9/45

-

US Classification:717158, 717145

-

Abstract:A method, system, and program product for optimizing compilation. In the preferred embodiment, a compiler compiles a source-code file twice; once to gather register-pressure data, and a second time to apply the data. Thus, the compiler saves register-pressure data during the first compilation and uses it during the second compilation to make informed inlining decisions. The compiler saves two kinds of data during the first compilation: (1) the maximum register-pressure occurring in each procedure; and (2) within each procedure, the register pressure at each call site that is a potential inlining candidate. This data is then fed into the compiler during the second compilation. The compiler uses the data during the second compilation in two ways. First, when deciding whether to inline a child procedure into a parent procedure, the compiler determines whether the sum of the maximum register-pressure and the site register-pressure exceeds the number of available, physical registers. If so, the inlining is not done.

-

Selecting A Target Number Of Pages For Allocation To A Partition

view source -

US Patent:8090911, Jan 3, 2012

-

Filed:Apr 16, 2009

-

Appl. No.:12/424772

-

Inventors:Wade B. Ouren - Rochester MN, US

Edward C. Prosser - Rochester MN, US

Kenneth C. Vossen - Rochester MN, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 12/04

-

US Classification:711129, 711153, 711170

-

Abstract:In an embodiment, a target number of discretionary pages for a first partition is calculated as a function of a number of physical page table faults, a number of sampled page faults, a number of shared physical page pool faults, a number of re-page-ins, and a ratio of pages. If the target number of discretionary pages for the first partition is less than a number of the discretionary pages that are allocated to the first partition, a result page is found that is allocated to the first partition and the result page is deallocated from the first partition. If the target number of discretionary pages for the first partition is greater than the number of the discretionary pages that are allocated to the first partition, a free page is allocated to the first partition.

-

Hypervisor Page Fault Processing In A Shared Memory Partition Data Processing System

view source -

US Patent:8166254, Apr 24, 2012

-

Filed:Mar 13, 2009

-

Appl. No.:12/403408

-

Inventors:David A. Larson - Rochester MN, US

Edward C. Prosser - Rochester MN, US

Kenneth C. Vossen - Rochester MN, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 12/00

-

US Classification:711148, 718104

-

Abstract:Hypervisor page fault processing logic is provided for a shared memory partition data processing system. The logic, responsive to an executing virtual processor of the shared memory partition data processing system encountering a hypervisor page fault, allocates an input/output (I/O) paging request to the virtual processor from an I/O paging request pool and increments an outstanding I/O paging request count for the virtual processor. A determination is then made whether the outstanding I/O paging request count for the virtual processor is at a predefined threshold, and if not, the logic places the virtual processor in a wait state with interrupt wake-up reasons enabled based on the virtual processor's state, otherwise, it places the virtual processor in a wait state with interrupt wake-up reasons disabled.

-

Hypervisor Page Fault Processing In A Shared Memory Partition Data Processing System

view source -

US Patent:8281082, Oct 2, 2012

-

Filed:Jan 31, 2012

-

Appl. No.:13/362402

-

Inventors:David A. Larson - Rochester MN, US

Edward C. Prosser - Rochester MN, US

Kenneth C. Vossen - Rochester MN, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 12/00

-

US Classification:711148, 711209

-

Abstract:Hypervisor page fault processing logic is provided for a shared memory partition data processing system. The logic, responsive to an executing virtual processor of the shared memory partition data processing system encountering a hypervisor page fault, allocates an input/output (I/O) paging request to the virtual processor from an I/O paging request pool and increments an outstanding I/O paging request count for the virtual processor. A determination is then made whether the outstanding I/O paging request count for the virtual processor is at a predefined threshold, and if not, the logic places the virtual processor in a wait state with interrupt wake-up reasons enabled based on the virtual processor's state, otherwise, it places the virtual processor in a wait state with interrupt wake-up reasons disabled.

-

Relocating Page Tables And Data Amongst Memory Modules In A Virtualized Environment

view source -

US Patent:8285915, Oct 9, 2012

-

Filed:Jan 13, 2010

-

Appl. No.:12/686681

-

Inventors:Stuart Z. Jacobs - Lakeville MN, US

David A. Larson - Rochester MN, US

Wade B. Ouren - Rochester MN, US

Edward C. Prosser - Rochester MN, US

Kenneth C. Vossen - Rochester MN, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 12/02

-

US Classification:711 6, 711206, 718105

-

Abstract:Relocating data in a virtualized environment maintained by a hypervisor administering access to memory with a Cache Page Table (‘CPT’) and a Physical Page Table (‘PPT’), the CPT and PPT including virtual to physical mappings. Relocating data includes converting the virtual to physical mappings of the CPT to virtual to logical mappings; establishing a Logical Memory Block (‘LMB’) relocation tracker that includes logical addresses of an LMB, source physical addresses of the LMB, target physical addresses of the LMB, a translation block indicator for each relocation granule, and a pin count associated with each relocation granule; establishing a PPT entry tracker including PPT entries corresponding to the LMB to be relocated; relocating the LMB in a number of relocation granules including blocking translations to the relocation granules during relocation; and removing the logical addresses from the LMB relocation tracker.

-

Dynamic Control Of Partition Memory Affinity In A Shared Memory Partition Data Processing System

view source -

US Patent:8312230, Nov 13, 2012

-

Filed:Mar 13, 2009

-

Appl. No.:12/403440

-

Inventors:Stuart Z. Jacobs - Lakeville MN, US

David A. Larson - Rochester MN, US

Wade B. Ouren - Rochester MN, US

Edward C. Prosser - Rochester MN, US

Kenneth C. Vossen - Rochester MN, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 12/00

G06F 13/00

G06F 13/28 -

US Classification:711153, 718104, 718105

-

Abstract:Dynamic control of memory affinity is provided for a shared memory logical partition within a shared memory partition data processing system having a plurality of nodes. The memory affinity control approach includes: determining one or more home node assignments for the shared memory logical partition, with each assigned home node being one node of the plurality of nodes of the system; determining a desired physical page level per node for the shared memory logical partition; and allowing the shared memory partition to run and using the home node assignment(s) and its desired physical page level(s) in the dispatching of tasks to physical processors in the nodes and in hypervisor page memory management to dynamically control memory affinity of the shared memory logical partition in the data processing system.

Resumes

Independent Affiliate

view sourceLocation:

P/O Box 5484, Burlington, VT

Industry:

Restaurants

Work:

Legalshield

Independent Affiliate

Espinola Donuts Dec 2015 - Jan 2018

Multi Unit Manager

Torgorm Property Services Dec 2015 - Jan 2018

Owner and Operator

Vermont Donut Jul 2015 - Dec 2015

Restaurant Manager

Jes Impresa Jan 2011 - Jul 2015

General Manager

Independent Affiliate

Espinola Donuts Dec 2015 - Jan 2018

Multi Unit Manager

Torgorm Property Services Dec 2015 - Jan 2018

Owner and Operator

Vermont Donut Jul 2015 - Dec 2015

Restaurant Manager

Jes Impresa Jan 2011 - Jul 2015

General Manager

Education:

New England Institute of Technology 1999 - 2000

East Providence Senior High School 1996 - 1999

East Providence Senior High School 1996 - 1999

Skills:

Restaurants

Restaurant Management

Food Service

Food Safety

Customer Service

Team Building

Management

Retail

Customer Satisfaction

Training

Sales

Food

Property Management

Property Preservation

Restaurant Management

Food Service

Food Safety

Customer Service

Team Building

Management

Retail

Customer Satisfaction

Training

Sales

Food

Property Management

Property Preservation

Owner At Prossertheriault Accounting

view sourceLocation:

New Brunswick, Canada

Industry:

Accounting

Software Engineer At Ibm

view sourceLocation:

Rochester, Minnesota Area

Industry:

Computer Software

Edward Prosser

view sourceName / Title

Company / Classification

Phones & Addresses

Owner

J & P Auto Repair (2008) Ltd.

Auto Repair & Service

Auto Repair & Service

274 Restigouche Road, Oromocto, NB E2V 2G9

(506)3572229

(506)3572229

Owner

J & P Auto Repair (2008) Ltd

Auto Repair & Service

Auto Repair & Service

(506)3572229

Classmates

Edward Prosser

view sourceSchools:

Ponce De Leon High School Ponce De Leon FL 1972-1976

Community:

Michael Busby

Edward Prosser

view sourceSchools:

Henderson High School Troy AL 1987-1991

Community:

Russell Kelly, Joyce Sneed

Edward Prosser, Nackawic,...

view sourceEdward Prosser 1981 graduate of Nackawic High School in Nackawic, NB

Ed Prosser, Spring valley...

view sourceEd Prosser 1995 graduating class of Spring Valley High School in Spring valley, WI

Ed Prosser, Wilkinsburg, PA

view sourceEd Prosser 1965 graduate of Wilkinsburg High School in Wilkinsburg, PA

Ed Prosser, Bloomington, IN

view sourceEd Prosser 1980 graduate of Bloomington High School South in Bloomington, IN

Henderson High School, Tr...

view sourceGraduates:

Denise Kingry (1979-1983),

Terry Ginyard (1989-1993),

Edward Prosser (1987-1991),

Judy Hutchison (1979-1983)

Terry Ginyard (1989-1993),

Edward Prosser (1987-1991),

Judy Hutchison (1979-1983)

Nackawic High School, Nac...

view sourceGraduates:

Edward Prosser (1977-1981),

Shane Brewer (1998-2002),

Rachel Baxter (1983-1987),

Maxine Brewer (1979-1983)

Shane Brewer (1998-2002),

Rachel Baxter (1983-1987),

Maxine Brewer (1979-1983)

Flickr

Edward Prosser

view source

Edward Prosser

view sourceFriends:

Natasha Lane, Kim Farmer, Wayne Griffiths, Joanne Danielle Thomas, David Smith

Ed Prosser

view sourceYoutube

Get Report for Edward C Prosser from Rochester, MN, age ~63