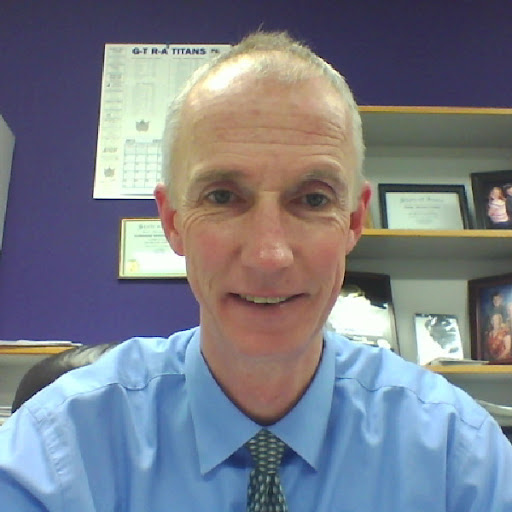

Jon E Josephson

age ~60

from Minneapolis, MN

- Also known as:

-

- Jon Eric Josephson

- Jon E Joesphson

- John Josephson

- Phone and address:

-

5412 Shoreview Ave, Minneapolis, MN 55417

(612)2260277

Jon Josephson Phones & Addresses

- 5412 Shoreview Ave, Minneapolis, MN 55417 • (612)2260277

- 2219 Creststone Ct, Fort Collins, CO 80525

- 2212 Vermont Dr, Fort Collins, CO 80525

- Eagan, MN

- Rosemount, MN

- Schenectady, NY

Resumes

Mixed Signal Ic Design Engineer At Honeywell

view sourceLocation:

Greater Minneapolis-St. Paul Area

Industry:

Electrical/Electronic Manufacturing

It Manager

view sourceLocation:

Grantsburg, WI

Industry:

Defense & Space

Work:

Mcnally Industries

It Manager

Ultra Tool Nov 1997 - Jan 2003

It Manager

Firstar May 1987 - Oct 1995

Retail Lender

It Manager

Ultra Tool Nov 1997 - Jan 2003

It Manager

Firstar May 1987 - Oct 1995

Retail Lender

Education:

University of Wisconsin - Eau Claire 1983 - 1988

Bachelors, Bachelor of Science, Finance

Bachelors, Bachelor of Science, Finance

Skills:

System Administration

Microsoft Exchange

Wireless Networking

Computer Repair

Help Desk Support

Telephony

Microsoft Office

Erp

Machine Control

Test Processes

Mixed Signal

Analog Circuit Design

Cmos

Analog

Ic

Semiconductors

Asic

Integrated Circuit Design

Debugging

Circuit Design

Testing

Microprocessors

Hardware Architecture

Fpga

Soc

Vlsi

Microsoft Exchange

Wireless Networking

Computer Repair

Help Desk Support

Telephony

Microsoft Office

Erp

Machine Control

Test Processes

Mixed Signal

Analog Circuit Design

Cmos

Analog

Ic

Semiconductors

Asic

Integrated Circuit Design

Debugging

Circuit Design

Testing

Microprocessors

Hardware Architecture

Fpga

Soc

Vlsi

Jon Josephson

view source

Jon Josephson

view sourceUs Patents

-

In-Place Method For Inserting Repeater Buffers In An Integrated Circuit

view source -

US Patent:6532580, Mar 11, 2003

-

Filed:Feb 18, 2000

-

Appl. No.:09/507034

-

Inventors:Jon Eric Josephson - Fort Collins CO

Jeffrey P Witte - Ft Collins CO

Rex Mark Petersen - Fort Collins CO -

Assignee:Hewlett-Packard Company - Palo Alto CA

-

International Classification:G06F 1750

-

US Classification:716 10, 716 12, 716 2

-

Abstract:A method and system for inserting in-place interconnect repeaters along the paths of interconnects of an integrated circuit is presented. The integrated circuit includes an interconnect layer on which an interconnect is routed, a silicon layer in which repeaters are implemented, and zero or more intervening layers. In accordance with the invention, reserved metal areas are defined on each intervening layer that resides between the interconnect layer and the repeater layer. Each interconnect net that requires a repeater for performance reasons is assigned to a repeater location. A repeater buffer is inserted at the assigned repeater locations. The interconnect net is cut into first and second subnets, which are then respectively connected through the reserved metal areas of the intervening layers to the respective input and output port of the repeater buffer.

-

Delay Locked Loop With Selectable Delay

view source -

US Patent:7323915, Jan 29, 2008

-

Filed:Jan 19, 2006

-

Appl. No.:11/335749

-

Inventors:Jon E. Josephson - Minneapolis MN, US

-

Assignee:Honeywell International, Inc. - Morristown NJ

-

International Classification:H03L 7/06

-

US Classification:327149, 327158

-

Abstract:A DLL includes a control module coupled with a phase detect signal. The phase detect signal is used by a control module to generate feedback and output select signals. The feedback and output select signals are each coupled to a multiplexer. Each multiplexer is coupled to a Multi-Tap Delay Line (MTDL). The MTDL provides a plurality of delayed signals that are selectable by the two multiplexers. The first multiplexer, coupled to the feedback select signal, selects a feedback clock signal. The second multiplexer, coupled to the output select signal, select a DLL output signal. The control module may receive other signals, such as a delay select signal, that may be used to program or set the delay of the output signal. In addition, a plurality of output signals may be available from the DLL.

-

Method For Determining Locations Of Interconnect Repeater Farms During Physical Design Of Integrated Circuits

view source -

US Patent:6408426, Jun 18, 2002

-

Filed:Feb 19, 2000

-

Appl. No.:09/507442

-

Inventors:Jon Eric Josephson - Fort Collins CO

John D Wanek - Denver CO -

Assignee:Hewlett-Packard Company - Palo Alto CA

-

International Classification:G06F 1750

-

US Classification:716 12, 716 9, 716 10

-

Abstract:A method and system for determining locations of interconnect repeater farms in the physical design of an integrated circuit is presented. The optimal unconstrained repeater locations are calculated for a given routing list of interconnect nets. Repeater farms are defined in areas of concentration of the calculated optimal unconstrained repeater locations. The optimal constrained repeater locations are then calculated such that the repeater locations are constrained to the repeater farms. A set of sub-optimal interconnect nets which are hurt the most from the repeater farm constraint are selected. The optimal unconstrained repeater locations for the selected set of sub-optimal interconnect nets are then calculated and additional repeater farms are defined to encompass areas of concentration of the optimal repeater locations of the sub-optimal interconnect nets. The process is repeated until desired performance gain is achieved.

Classmates

John Josephs Denfeld Hig...

view sourceJohn Josephson 1959 graduate of Denfeld High School in Duluth, MN is on Memory Lane. Get caught up with John and other high school alumni from Denfeld High

Jon Josephson

view sourceSchools:

Albert City-Truesdale High School Albert City IA 1971-1984

Community:

Tina Hand

Jon Josephson

view sourceSchools:

Cloquet High School Cloquet MN 1989-1993

John Josephson | Clevelan...

view source

John Josephson, Calhan Mi...

view source

John Josephson | James Ma...

view source

Albert City-Truesdale Hig...

view sourceGraduates:

Jon Josephson (1971-1984),

Jeff Emery (1975-1988),

Terry Nordine (1971-1975),

Tricia Hogrefe (2003-2007),

Diane Balder (1968-1972)

Jeff Emery (1975-1988),

Terry Nordine (1971-1975),

Tricia Hogrefe (2003-2007),

Diane Balder (1968-1972)

Westmar College, Le mars,...

view sourceGraduates:

Jon Josephson (1984-1989),

Becky Young (1980-1981),

Avalyn Dillingham (1958-1962),

Ron Wikstrom (1958-1962)

Becky Young (1980-1981),

Avalyn Dillingham (1958-1962),

Ron Wikstrom (1958-1962)

Jon Josephson

view source

Jon Josephson

view sourceMyspace

Youtube

Googleplus

Jon Josephson

Jon Josephson

Flickr

Get Report for Jon E Josephson from Minneapolis, MN, age ~60