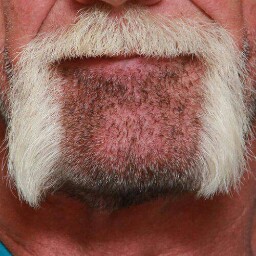

Michael A Minter

age ~61

from Bowling Green, KY

- Also known as:

-

- Mike Minter

- Phone and address:

-

1262 Chestnut St, Bowling Green, KY 42101

(270)4219550

Michael Minter Phones & Addresses

- 1262 Chestnut St, Bowling Green, KY 42101 • (270)4219550

- McLean, VA

- Fairfax, VA

- Raleigh, NC

Work

-

Address:Suite 500 1751 Pinnacle Drive, Mclean, VA 22102

Ranks

-

Licence:Virginia - Authorized to practice law

-

Date:2001

Isbn (Books And Publications)

License Records

Michael R Minter

License #:

1112 - Active

Category:

Polygraph Examiner

Expiration Date:

Dec 31, 2017

Name / Title

Company / Classification

Phones & Addresses

MINTER MFG

Iron Work

Iron Work

1112 Sands Pines Crescent, Comox, BC V9M 3V3

(250)3391377

(250)3391377

MINTER MFG

Iron Work

Iron Work

(250)3391377

Director, Vice-President

Fairfax Bar Association

Legal Services · Professional Organization Legal Services Office

Legal Services · Professional Organization Legal Services Office

4110 Chain Brg Rd #303, Fairfax, VA 22030

(703)2462740

(703)2462740

Us Patents

-

System For Performing Automatic Test Pin Assignment For A Programmable Device

view source -

US Patent:7290194, Oct 30, 2007

-

Filed:Dec 17, 2004

-

Appl. No.:11/016192

-

Inventors:Donald Gabrielson - Rochester MN, US

Todd Youngman - Rochester MN, US

John Nordman - Rochester MN, US

Michael A. Minter - Bowling Green KY, US -

Assignee:LSI Corporation - Milpitas CA

-

International Classification:G01R 31/28

-

US Classification:714742

-

Abstract:A tool for facilitating automatic test pin assignment for a programmable platform device including a process for collecting information related to the programmable platform device, a process for automatically initializing a test pin assignment for the programmable platform device, a process configured to receive user specifications for IOs and a process for performing dynamic test pin reassignment in response to the user specifications.

-

Automated Timing Optimization

view source -

US Patent:8336012, Dec 18, 2012

-

Filed:Apr 9, 2009

-

Appl. No.:12/421198

-

Inventors:Randall P. Fry - Greenville NC, US

Michael A. MInter - Bowling Green KY, US -

Assignee:LSI Corporation - Milpitas CA

-

International Classification:G06F 9/455

G06F 17/50 -

US Classification:716113, 716108, 716111, 716112, 716134, 703 19

-

Abstract:A method for reducing a timing violation in a negative slack path from an integrated circuit design, by identifying the negative slack path in the integrated circuit design with a processor, and then identifying positive slack paths by determining timing slack for the paths that are disposed before and after the negative slack path. A prediction is made as to whether margin can be obtained from the positive slack paths by performing additional timing optimization on the positive slack paths, and it is determined whether that margin is sufficient to reduce the timing violation to at least a desired level. If the margin is sufficient, then additional timing optimization is performed on the positive slack paths, and the margin is used to manipulate the clock skew and reduce the timing violation on the negative slack path.

-

Timing Constraint Generator

view source -

US Patent:20040268279, Dec 30, 2004

-

Filed:Jun 24, 2003

-

Appl. No.:10/602937

-

Inventors:Nicholas Oleksinski - Northville MI, US

Michael Minter - Bowling Green KY, US -

Assignee:LSI LOGIC CORPORATION

-

International Classification:G06F009/45

-

US Classification:716/006000

-

Abstract:A method for generating a plurality of timing constraints for a circuit design is disclosed. The method generally includes the steps of (A) identifying a plurality of clock signals by analyzing the circuit design, (B) determining a plurality of relationships among the clock signals and (C) generating the timing constraints for the circuit design in response to the clock signals and the relationships.

-

Macro Block Placement By Pin Connectivity

view source -

US Patent:20070044056, Feb 22, 2007

-

Filed:Aug 16, 2005

-

Appl. No.:11/204514

-

Inventors:Michael Minter - Bowling Green KY, US

Donald Amundson - New Prague MN, US

Donald Gabrielson - Rochester MN, US -

International Classification:G06F 17/50

-

US Classification:716008000

-

Abstract:A design tool includes a first module, a second module, a third module and a fourth module. The first module may be configured to select a platform for implementing an integrated circuit design in response to input from a user. The second module may be configured to select a macro block to be placed on the platform in response to input from the user. A description of the macro block may be configured to indicate whether the macro block has connectivity placement data. The third module may be configured to determine whether the macro block has the connectivity placement data based on the description of the macro block. The fourth module may be configured to automatically place the macro block on the platform based on the connectivity placement data, when the description of the macro block indicates the connectivity placement data is present.

Lawyers & Attorneys

Michael Allan Minter, McLean VA - Lawyer

view sourceAddress:

Suite 500 1751 Pinnacle Drive, Mclean, VA 22102

(703)9039000 (Office)

(703)9039000 (Office)

Licenses:

Virginia - Authorized to practice law 2001

Resumes

Distinguished Engineer

view sourceLocation:

509 Loma Vis, Rockwall, TX 75032

Industry:

Semiconductors

Work:

Western Kentucky University Research Foundation

Member Board of Directors

Ge Microelectronics Center Jul 1986 - Oct 1988

Design Engineer

Broadcom Jul 1986 - Oct 1988

Distinguished Engineer

Member Board of Directors

Ge Microelectronics Center Jul 1986 - Oct 1988

Design Engineer

Broadcom Jul 1986 - Oct 1988

Distinguished Engineer

Education:

University of Tennessee, Knoxville 1982 - 1986

Bachelors, Bachelor of Science In Electrical Engineering, Computer Engineering

Bachelors, Bachelor of Science In Electrical Engineering, Computer Engineering

Skills:

Static Timing Analysis

Physical Design

Asic

Soc

Eda

Timing Closure

Semiconductors

Ic

Primetime

Vlsi

Tcl

Verilog

Dft

Serdes

Low Power Design

Integrated Circuit Design

Integrated Circuits

Rtl Design

Cmos

Debugging

Perl

Functional Verification

Logic Design

Signal Integrity

Circuit Design

Rtl Coding

Application Specific Integrated Circuits

Floorplanning

Formal Verification

Semiconductor Industry

Pcie

Physical Verification

Drc

Lvs

Clock Tree Synthesis

Power Analysis

Place and Route

Synopsys Tools

Cadence

Timing

Atpg

Gnu Make

Bist

Power Management

Physical Design

Asic

Soc

Eda

Timing Closure

Semiconductors

Ic

Primetime

Vlsi

Tcl

Verilog

Dft

Serdes

Low Power Design

Integrated Circuit Design

Integrated Circuits

Rtl Design

Cmos

Debugging

Perl

Functional Verification

Logic Design

Signal Integrity

Circuit Design

Rtl Coding

Application Specific Integrated Circuits

Floorplanning

Formal Verification

Semiconductor Industry

Pcie

Physical Verification

Drc

Lvs

Clock Tree Synthesis

Power Analysis

Place and Route

Synopsys Tools

Cadence

Timing

Atpg

Gnu Make

Bist

Power Management

Languages:

English

Michael Minter

view source

Michael Minter

view source

Michael Minter

view source

Michael Minter

view source

Michael Minter

view source

Ror Developer

view sourcePosition:

Senior Developer at SiteFM

Location:

Austin, Texas

Industry:

Program Development

Work:

SiteFM - Austin, Texas Area since Dec 2011

Senior Developer

TWG Plus - Austin, Texas Area Aug 2010 - Jan 2012

Lead Developer

Moorberry Solutions - Austin, Texas Area Jan 2009 - Sep 2010

Owner

Senior Developer

TWG Plus - Austin, Texas Area Aug 2010 - Jan 2012

Lead Developer

Moorberry Solutions - Austin, Texas Area Jan 2009 - Sep 2010

Owner

Education:

DeVry University-Texas 2006 - 2008

Computer Information Systems, Computer Programming

Computer Information Systems, Computer Programming

Skills:

Ruby on Rails

MySQL

Git

Web Development

JavaScript

jQuery

API

Big Data

Database Modeling

SendGrid

Project Management

SQLite

MongoDB

HTML + CSS

REST

PayPal

Authorize.net

Email Marketing

JSON

Web Applications

HTML5

Linux

MVC

Amazon Web Services

Web Services

Open Source

Agile

SQL

Highcharts

jQuery Mobile

PostgreSQL

RVM

Technical Direction

Technical Training

Ruby

Twilio

Sinatra

Google Analytics

MySQL

Git

Web Development

JavaScript

jQuery

API

Big Data

Database Modeling

SendGrid

Project Management

SQLite

MongoDB

HTML + CSS

REST

PayPal

Authorize.net

Email Marketing

JSON

Web Applications

HTML5

Linux

MVC

Amazon Web Services

Web Services

Open Source

Agile

SQL

Highcharts

jQuery Mobile

PostgreSQL

RVM

Technical Direction

Technical Training

Ruby

Twilio

Sinatra

Google Analytics

Interests:

web applications, big data, collecting bugs

Awards:

Twilio API Contest Winner

Twilio

Awarded for excellence in utilizing the Twilio API at the 2011 FridayNightHacks Code Contest in Austin, Texas. (github: Amburoads)

Top 100 Programmers to Follow

hackingtravel.com

Listed in “The Top Programmers in the World Who Will Still Answer Your Call” by hackingtravel.com

Top 10% Githubbers

githire.com

Listed as “top 10% of GitHub Users by estimated expertise” by githire.com

Twilio

Awarded for excellence in utilizing the Twilio API at the 2011 FridayNightHacks Code Contest in Austin, Texas. (github: Amburoads)

Top 100 Programmers to Follow

hackingtravel.com

Listed in “The Top Programmers in the World Who Will Still Answer Your Call” by hackingtravel.com

Top 10% Githubbers

githire.com

Listed as “top 10% of GitHub Users by estimated expertise” by githire.com

Michael Minter

view sourceLocation:

United States

Myspace

Googleplus

Michael Minter

Education:

Johnston high school

Tagline:

Stunning looks

Michael Minter

Tagline:

A.K.A Minterbomb, M C Lovin

Bragging Rights:

Ha! What isn't cool about me?

Michael Minter

Michael Minter

About:

Head of communications and project manager at CONCITOFounder and moderator of Ecoprofile DanmarkOwner of ECOPA Sustainability Consulting

Tagline:

Green strategist, entrepreneur and communicator

Michael Minter

Michael Minter

Michael Minter

Michael Minter

Flickr

Plaxo

Michael Minter

view sourceMagician / Illusions at Master Magician Master Magician, Michael has been performing for over 20 years. He has performed in both Ulster and Dutchess counties. Michael takes his show to the max with... Master Magician, Michael has been performing for over 20 years. He has performed in both Ulster and Dutchess counties. Michael takes his show to the max with out-standing magic and illusions, Live doves, music, comdey, and audience participation.

Classmates

Michael Minter

view sourceSchools:

Annunciation School Arcadia CA 1981-1985

Community:

Steve Olsen, Ray Onisko, Marguerita Clements

Michael L Minter

view sourceSchools:

Coolidge High School Coolidge AZ 1968-1972

Community:

Wayne Wilber, Ardith Walthers, Peggy Patterson, Kay Lantz

Michael Minter

view sourceSchools:

St. Benedict School Philadelphia PA 1972-1980

Community:

Joseph Wright, John Toth

Michael Minter

view sourceSchools:

State Park Elementary School Collinsville IL 1955-1962, North Junior High School Collinsville IL 1962-1965

Community:

Darlene Coomes

Michael Minter, Williamso...

view source

Michael Minter | Des Moin...

view source

St. Benedict School, Phil...

view sourceGraduates:

Cayande Beaty (1985-1991),

Michael Minter (1976-1980),

Margaret McLaughlin (1959-1965)

Michael Minter (1976-1980),

Margaret McLaughlin (1959-1965)

Divine Word High School, ...

view sourceGraduates:

Michael Minter (1980-1984),

Patrick Connell (1965-1969)

Patrick Connell (1965-1969)

Youtube

Michael Minter

view source

Michael Minter

view source

Michael Minter

view source

Michael Minter

view source

Michael Minter

view source

Michael Minter

view source

Michael Blair Minter

view source

Michael M. Minter

view sourceGet Report for Michael A Minter from Bowling Green, KY, age ~61