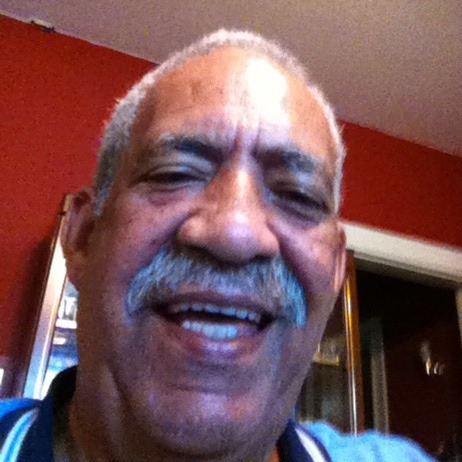

Reginald Jay Allen

age ~61

from Canyon Country, CA

- Also known as:

-

- Reginald Jaymes Allen

- Reginald J Allen

- James R Allen

- Lalcoc R Allen

- Reginal D Allen

- Jaymes R Allen

- Jayme S Allen

- Allen Jaymes

- James Mines

Reginald Allen Phones & Addresses

- Canyon Country, CA

- Las Vegas, NV

- Canoga Park, CA

- Los Angeles, CA

- Inglewood, CA

- Ontario, CA

- Hawthorne, CA

Isbn (Books And Publications)

License Records

Reginald A. Allen

License #:

MD02209 - Expired

Category:

Physician

Issued Date:

Apr 15, 1935

Expiration Date:

Jan 1, 1997

Type:

Allopathic Physician (MD)

Name / Title

Company / Classification

Phones & Addresses

Director

Global Industrial Services, Inc

PO Box 27740, Las Vegas, NV 89126

Us Patents

-

Ccd Frequency Divider Circuit

view source -

US Patent:42490928, Feb 3, 1981

-

Filed:Oct 9, 1979

-

Appl. No.:6/083042

-

Inventors:Reginald A. Allen - Los Angeles CA

-

Assignee:TRW Inc. - Redondo Beach CA

-

International Classification:G11C 1928

H01L 2978 -

US Classification:307221D

-

Abstract:A charge coupled device (CCD) frequency divider circuit for dividing the frequency of an input signal comprises a CCD having main, drain, and feedback channels. Input signal charge is injected during each cycle of the input signal into a potential well under a storage electrode that retains a predetermined quantity of charge. Overflow from the storage electrode is detected by a sensing electrode that is normally maintained in a transfer state, causing the sensing electrode to switch to a barrier state. This allows the predetermined quantity of charge to advance to an output while the overflow is dumped out by the drain channel. However, when no overflow is present, the sensing electrode causes the input charge to be transferred into the feedback channel which circulates it to the storage electrode to combine with another input charge received by the storage electrode during a subsequent cycle of the input signal. The feedback channel includes delay electrodes which delay the charge in the feedback channel from combining with the input charge until a predetermined number of cycles of the input signal have passed. The frequency of the input signal is divided by an even number dependent upon the number of cycles by which the delay electrodes delay the charge in the feedback channel from combining with a new input charge to give a whole number of output cycles.

-

Charge Coupled Device Channel Crossover Circuit

view source -

US Patent:42373891, Dec 2, 1980

-

Filed:Sep 1, 1978

-

Appl. No.:5/938911

-

Inventors:Reginald A. Allen - Topanga CA

-

Assignee:TRW Inc. - Redondo Beach CA

-

International Classification:G11C 1928

H01L 2978 -

US Classification:307221D

-

Abstract:A charge coupled device channel crossover circuit transfers charge packets in each of two different intersecting channels during each of a succession of transfer intervals defined by a pair of clocking signals of opposite phase and a pair of clock signal related pulse trains applied to various electrodes of the crossover circuit to provide changing potential biases. The crossover circuit includes a common transfer area at the intersection of the two channels, a pair of transfer gates within each channel on opposite sides of the transfer area and a pair of storage areas within each channel on opposite sides of the transfer gates from the transfer area. During each transfer interval a charge packet introduced at the input end of one of the channels is transferred through the intersection to the output end of the channel by the changing potential biases, following which a charge packet introduced into the input end of the other channel is transferred through the intersection to the output end of the other channel by bias level changes. The changes in bias level provided by the clocking signals and the pulse trains advance the charge packets through the intersection without interference from one another and so that each charge packet is prevented from traveling in a wrong direction or from entering the other one of the channels.

-

Latch Circuit For Digital Charge Coupled Systems

view source -

US Patent:42386934, Dec 9, 1980

-

Filed:Sep 1, 1978

-

Appl. No.:5/938952

-

Inventors:Reginald A. Allen - Topanga CA

-

Assignee:TRW Inc. - Redondo Beach CA

-

International Classification:G11C 1928

H01L 2978

H03K 1920 -

US Classification:307221D

-

Abstract:A circuit for use in digital charge coupled systems provides successive indications of input binary value, until reset, without timing delays and without degeneration of the charge packets. A data input charge packet is provided to a storage electrode, and a series of standardized charge packets are also provided to the storage electrode at the data rate of the system. The latch circuit operates cyclically in internal cycles between the arrival of successive standardized charge packets. The concurrent presence of an input charge packet and a standardized charge packet results in charge overflow across a barrier in a first output data channel. This overflow causes a floating gate electrode that interconnects the first output channel with a second output channel to block transfer of the basic charge packet out the second output channel. It also causes the basic charge packet to be returned as a data input back to the storage electrode. With the basic charge packet representing a binary "1", therefore, the recirculation is effected with each arrival of a new standardized data packet.

Resumes

At Us Navy

view sourceLocation:

United States

Reginald Allen

view sourceLocation:

United States

Reginald Allen

view sourceLocation:

United States

Reginald Allen

view sourceLocation:

United States

Reginald Allen

view sourceLocation:

United States

Reginald Allen

view sourceLocation:

United States

Reginald Allen

view sourceLocation:

United States

Classmates

Reginald Allen

view sourceSchools:

Friendly High School Ft. Washington MD 2001-2005

Community:

Marc Ferrara, Jeffrey Bolton, Cindi Jones

Reginald Allen

view sourceSchools:

Farmington High School Farmington MI 1994-1998

Community:

Lori Steele, Marsha Goodhue, Jerry Andrews, Patty Pawlus

Reginald Allen

view sourceSchools:

Friendly High School Ft. Washington MD 2001-2005

Community:

Marc Ferrara, Jeffrey Bolton, Cindi Jones

Reginald Allen

view sourceSchools:

South Burlington High School South Burlington VT 2002-2006

Community:

Karen Trueman, Edna Marshall, Amanda Bessette

Reginald Allen

view sourceSchools:

Pineview High School Lisbon LA 1981-1985

Community:

Terry Bedford, Terence Mitchell

Reginald Allen

view sourceSchools:

New Jersey Avenue Elementary School Atlantic City NJ 1950-1957, Chelsea Heights Elementary School Atlantic City NJ 1958-1960

Community:

Marva Jones, George Batten

Reginald Allen

view sourceSchools:

Dupo Junior High School Dupo IL 1993-1995

Community:

Rick King, Linda Bradley, Lynn Duty, Curtis Steward

Reginald Allen

view sourceSchools:

Eisenhower High School Houston TX 1983-1987

Community:

Bruce Cyphers, Nancy Personette

Myspace

Reginald Allen

view sourceGender:

Male

Youtube

Flickr

Reginald Allen Tadic

view source

Reginald BigMeechie Allen

view source

Reginald Butta Allen

view source

Reginald J. Allen

view source

Reginald Slugger Allen

view source

Reginald Allen Harris

view source

Reginald Allen

view source

Reginald Allen

view sourceGoogleplus

Reginald Allen

Reginald Allen

Reginald Allen

Reginald Allen

Reginald Allen

Reginald Allen

Reginald Allen

Reginald Allen

Get Report for Reginald Jay Allen from Canyon Country, CA, age ~61