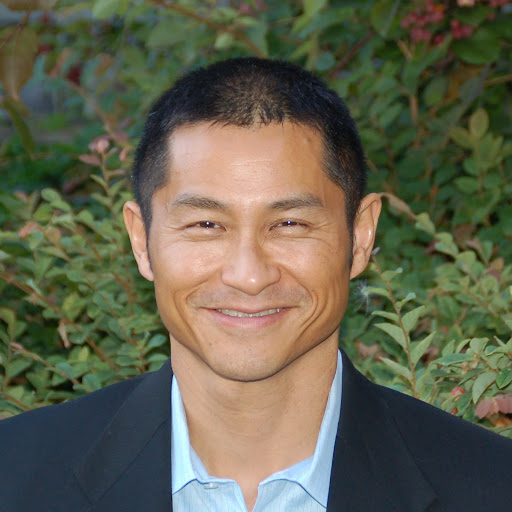

Yen H Lee

age ~53

from San Francisco, CA

- Also known as:

-

- Yen Hung Lee

- Yen T Lee

- Hung Yen Lee

- Hung Y Lee

- Hung Lee Yen

- Hoang Le

- Hoan G Le

- Lee Yen

- Phone and address:

-

278 Victoria St, San Francisco, CA 94132

(415)6520227

Yen Lee Phones & Addresses

- 278 Victoria St, San Francisco, CA 94132 • (415)6520227

- Oakland, CA

- Daly City, CA

Lawyers & Attorneys

Yen Yao Lee - Lawyer

view sourceLicenses:

Dist. of Columbia - Active 2007

Us Patents

-

Content Service Aggregation Device For A Data Center

view source -

US Patent:7363353, Apr 22, 2008

-

Filed:Jul 8, 2002

-

Appl. No.:10/191746

-

Inventors:Elango Ganesan - Palo Alto CA, US

Ramesh Panwar - Pleasanton CA, US

Yen Lee - San Jose CA, US

Chau Anh Ngoc Nguyen - San Jose CA, US

John Phillips - Santa Clara CA, US

Yuhong Andy Zhou - Alameda CA, US

Gregory G Spurrier - Sunnyvale CA, US

Michael Freed - Pleasanton CA, US

Mark Bryers - Granite Bay CA, US

Nazar Zaidi - San Jose CA, US -

Assignee:Juniper Networks, Inc. - Sunnyvale CA

-

International Classification:G06F 15/16

-

US Classification:709218, 709203, 709201, 370235

-

Abstract:An architecture for controlling a multiprocessing system to provide at least one network service to subscriber data packets transmitted in the system using a plurality of compute elements, comprising a management compute element including service set-up information for at least one service and at least one processing compute element applying said at least one network service to said data packets and communicating service set-up information with the management compute element in order to perform service specific operations on data packets. In a further embodiment, a method of controlling a processing system including a plurality of processors is disclosed. The method comprises the steps of operating at least one of said processors as a control authority providing service provisioning information for a subscriber; and operating a set of processors as a service specific compute element responsive to the control authority, receiving provisioning information from the subscriber and performing service specific instructions on data packets to provide IP content services.

-

Content Service Aggregation System

view source -

US Patent:20130155861, Jun 20, 2013

-

Filed:Feb 4, 2013

-

Appl. No.:13/758878

-

Inventors:JUNIPER NETWORKS, INC. - Sunnyvale CA, US

Elango Ganesan - Palo Alto CA, US

Frederick Gruner - Palo Alto CA, US

David Hass - Santa Clara CA, US

Robert Hathaway - Sunnyvale CA, US

Ramesh Panwar - Pleasanton CA, US

Ricardo Ramirez - Sunnyvale CA, US

Abbas Rashid - Fremont CA, US

Mark Vilas - San Jose CA, US

Nazar Zaidi - San Jose CA, US

Yen Lee - San Jose CA, US

Chau Anh Ngoc Nguyen - San Jose CA, US

John Phillips - Santa Clara CA, US

Yuhong Zhou - Alameda CA, US

Gregory G. Spurrier - Sunnyvale CA, US

Michael Freed - Fremont CA, US -

Assignee:JUNIPER NETWORKS, INC. - Sunnyvale CA

-

International Classification:H04L 12/56

-

US Classification:370235

-

Abstract:A network content service apparatus includes a set of compute elements adapted to perform a set of network services; and a switching fabric coupling compute elements in said set of compute elements. The set of network services includes firewall protection, Network Address Translation, Internet Protocol forwarding, bandwidth management, Secure Sockets Layer operations, Web caching, Web switching, and virtual private networking. Code operable on the compute elements enables the network services, and the compute elements are provided on blades which further include at least one input/output port.

-

Software For Producing Instructions In A Compressed Format For A Vliw Processor

view source -

US Patent:57873020, Jul 28, 1998

-

Filed:May 15, 1996

-

Appl. No.:8/649731

-

Inventors:Hari Hampapuram - Sunnyvale CA

Yen C. Lee - San Jose CA

Eino Jacobs - Palo Alto CA

Michael Ang - Santa Clara CA -

Assignee:Philips Electronic North America Corporation - New York NY

-

International Classification:G06F 700

-

US Classification:39580024

-

Abstract:Software creates a compressed instruction format for a VLIW processor which allows greater efficiency in use of cache and memory. Instructions are byte aligned and variable length. Branch targets are uncompressed. Format bits specify how many issue slots are used in a following instruction. NOPS are not stored in memory. Individual operations are compressed according to features such as whether they are resultless, guarded, short, zeroary, unary, or binary. Instructions are stored in compressed form in memory and in cache. Instructions are decompressed on the fly after being read out from cache.

-

Compiler Generating Swizzled Instructions Usable In A Simplified Cache Layout

view source -

US Patent:58623981, Jan 19, 1999

-

Filed:May 15, 1996

-

Appl. No.:8/649732

-

Inventors:Hari Hampapuram - Sunnyvale CA

Yen C. Lee - Sunnyvale CA

Michael Ang - Santa Clara CA

Eino Jacobs - Palo Alto CA -

Assignee:Philips Electronics North America Corporation - New York NY

-

International Classification:G06F 1300

-

US Classification:39580024

-

Abstract:The software which produces a shuffled bit stream which bit stream allows for a simplified cache layout. This object is met using computer software which includes code for receiving a compiled and linked object module produced by a compiler and/or linker and code for swizzling the compiled and linked software to produce a second object module. The second object module is suitable for being deswizzled upon reading from a cache memory using a cache structure whose output bus wires are not crossed.

-

Method And Apparatus For Custom Operations Of A Processor

view source -

US Patent:59637447, Oct 5, 1999

-

Filed:Apr 30, 1997

-

Appl. No.:8/836852

-

Inventors:Gerrit Ary Slavenburg - Los Altos CA

Pieter van der Meulen - Sunnyvale CA

Yong Cho - Princeton NJ

Vijay K. Mehra - Fremont CA

Yen C. Lee - San Jose CA -

Assignee:Philips Electronics North America Corporation - New York NY

-

International Classification:G06F 1516

G06F 1580

G06F 1716 -

US Classification:39580009

-

Abstract:Custom operations are useable in processor systems for performing functions including multimedia functions. These custom operations enhance a system, such as PC system, to provide real-time multimedia capabilities while maintaining advantages of a special-purpose, embedded solution, i. e. , low cost and chip count, and advantages of a general-purpose processor reprogramability. These custom operations work in a computer system which supplies input data having operand data, performs operations on the operand data, and supplies result data to a destination register. Operations performed may include audio and video processing including clipping or saturation operations. The present invention also performs parallel operations on select operand data from input registers and stores results in the destination register.

-

Method And Apparatus For Custom Operations

view source -

US Patent:61416754, Oct 31, 2000

-

Filed:Aug 30, 1996

-

Appl. No.:8/706059

-

Inventors:Gerrit Ary Slavenburg - Los Altos CA

Pieter van der Muelen - Sunnyvale CA

Yong H. Cho - Princeton NJ

Vijay K. Mehra - Freemont CA

Yen C. Lee - San Jose CA -

Assignee:Philips Electronics North America Corporation - New York NY

-

International Classification:G06F 750

G06F 752 -

US Classification:708706

-

Abstract:Custom operations are useable in processor systems for performing functions including multimedia functions. These custom operations enhance a system, such as PC system, to provide real-time multimedia capabilities while maintaining advantages of a special-purpose, embedded solution, i. e. , low cost and chip count, and advantages of a general-purpose processor reprogramability. These custom operations work in a computer system which supplies input data having at least two operand data, performs operations on the operand data, and supplies result data to a destination register.

-

Compressed Instruction Format For Use In A Vliw Processor And Processor For Processing Such Instructions

view source -

US Patent:58782672, Mar 2, 1999

-

Filed:May 29, 1998

-

Appl. No.:/086696

-

Inventors:Hari Hampapuram - Sunnyvale CA

Yen C Lee - San Jose CA

Eino Jacobs - Palo Alto CA

Michael Ang - Santa Clara CA -

Assignee:Philips Electronics North America Corporation - New York NY

-

International Classification:G06F 700

-

US Classification:39580024

-

Abstract:Software creates a compressed instruction format for a VLIW processor which allows greater efficiency in use of cache and memory. Instructions are byte aligned and variable length. Branch targets are uncompressed. Format bits specify how many issue slots are used in a following instruction. NOPS are not stored in memory. Individual operations are compressed according to features such as whether they are resultless, guarded, short, zeroary, unary, or binary. Instructions are stored in compressed form in memory and in cache. Instructions are decompressed on the fly after being read out from cache.

-

Method And System For Presence Detection

view source -

US Patent:20160078484, Mar 17, 2016

-

Filed:Nov 25, 2015

-

Appl. No.:14/952822

-

Inventors:- Redwood City CA, US

Steven Stanek - Fremont CA, US

Yen C. Lee - San Jose CA, US -

International Classification:G06Q 30/02

G01S 15/04 -

Abstract:Various presence detection techniques are disclosed. In some embodiments, a system comprises a signal generator configured to generate a signal that includes a plurality of selected frequencies that are selected from among a set of candidate frequencies, wherein inclusion or exclusion of each candidate frequency in the signal encodes a bit of information and wherein the encoded information comprises a store identifier that identifies a retail store; and a transmitter configured to transmit the signal within the retail store; wherein presence of a device in the retail store is determined in response to reception of the signal at the device and extraction of the store identifier from the received signal by decoding the received signal.

Name / Title

Company / Classification

Phones & Addresses

Little Red Dot Kitchen, LLC

Manufacture and Distribution of Specialt · The Manufacture and Distribution of Spec

Manufacture and Distribution of Specialt · The Manufacture and Distribution of Spec

1537 Barton Dr, Sunnyvale, CA 94087

839 S Mary Ave, Sunnyvale, CA 94087

839 S Mary Ave, Sunnyvale, CA 94087

President

Yen & Assoc

Accounting/Auditing/Bookkeeping · Accountant

Accounting/Auditing/Bookkeeping · Accountant

328 S Abbott Ave, Milpitas, CA 95035

(408)2631040

(408)2631040

Co-Founder

Uptake Networks, Inc

Commercial Nonphysical Research

Commercial Nonphysical Research

1134 Crane St, Menlo Park, CA 94025

Senior Manager/lead Architech

CAVIUM NETWORKS

Semiconductor and Related Device Manufacturing · Computer Systems Design Svcs

Semiconductor and Related Device Manufacturing · Computer Systems Design Svcs

805 E Middlefield Rd, Mountain View, CA 94043

(650)6259750, (650)6237000, (650)6259751

(650)6259750, (650)6237000, (650)6259751

President

INTERNATIONAL EQUIPMENT & TRADING CORP

2027 Emerson St, Palo Alto, CA 94301

Principal

Spark Search

Communication Services Telephone Communications

Communication Services Telephone Communications

654 High St, Palo Alto, CA 94301

Managing

415MEGABITS LLC

Iphone Application Development

Iphone Application Development

1390 Market St, San Francisco, CA 94102

Medicine Doctors

Yen Chich Lee

view sourceSpecialties:

Anesthesiology

Pain Medicine

Pain Medicine

Pain Medicine

Pain Medicine

Education:

China Medical University (1968)

Resumes

Financial Analyst At Wageworks

view sourcePosition:

FP&A at WageWorks

Location:

San Francisco Bay Area

Industry:

Banking

Work:

WageWorks since Apr 2011

FP&A

Wells Fargo Bank Jun 2010 - Mar 2011

Financial Analyst (contractor)

Bank of the West Oct 2009 - Feb 2010

Financial Analyst (contractor)

WaMu Card Services Sep 2006 - Jan 2009

Financial, Planning, and Analyst II

World Vision International Oct 2004 - Sep 2006

Sr. Treasury Analyst

FP&A

Wells Fargo Bank Jun 2010 - Mar 2011

Financial Analyst (contractor)

Bank of the West Oct 2009 - Feb 2010

Financial Analyst (contractor)

WaMu Card Services Sep 2006 - Jan 2009

Financial, Planning, and Analyst II

World Vision International Oct 2004 - Sep 2006

Sr. Treasury Analyst

Education:

Pepperdine University, The George L. Graziadio School of Business and Management

Master of Business Administration (MBA)

Master of Business Administration (MBA)

Skills:

Treasury Management

Cash Management

Strategic Financial Planning

Financial Reporting

Financial Services

Analysis

Finance

Account Reconciliation

Financial Accounting

Cash Management

Strategic Financial Planning

Financial Reporting

Financial Services

Analysis

Finance

Account Reconciliation

Financial Accounting

Yen Lee

view sourceLocation:

United States

Creative At Jumpstart Automotive Media

view sourcePosition:

Creative at Jumpstart Automotive Media

Location:

San Francisco Bay Area

Industry:

Media Production

Work:

Jumpstart Automotive Media

Creative

Creative

Googleplus

Yen Lee

Lived:

Palo Alto, CA

Tagline:

I believe in the magical and mythical power of dark chocolate

Yen Lee

Work:

The Beach Club - Big Slacker

Yen Lee

Yen Lee

Yen Lee

Yen Lee

Yen Lee

Yen Lee

Myspace

Yen Theng Lee

view source

Yen Lee Lumidao

view source

Yen Chung Lee

view source

Lim Yen Lee

view source

Yen Kung Lee

view source

Yen Lee

view source

Yen Ying Lee

view source

Kathy Yen Lee

view sourceClassmates

Yen Lee

view sourceSchools:

Holy Comforter Episcopal School Tallahassee FL 1985-1988, North Florida Christian School Tallahassee FL 1987-1995, North Florida Christian High School Tallahassee FL 1988-1992

Community:

Doug Williams, Annette Barineau, Kristen Bremer

Yen Ling Lee

view sourceSchools:

Pittsburgh Technical Institute High School Pittsburgh PA 1997-2001

Community:

Patricia Veith, Jamie Amos, David Lightowler, Thomas Crowder, Veronica Stevenson

Yen Lun Lee

view sourceSchools:

St. Ignatius High School Taipei GA 1984-1986

Community:

Rich Klucsarits, Martin Fu, Kai Tsai, David Chen, Chyuan Chou

Yen Lee

view sourceSchools:

Sudbury High School Sudbury Morocco 1967-1971

Community:

Brian Green, Marilyn Decarle, Richard Martin

North Florida Christian S...

view sourceGraduates:

Yen Lee (1987-1995),

Elizabeth Harrington (2004-2008),

Judy Poppell (1969-1973),

Debbie Watson (1969-1973)

Elizabeth Harrington (2004-2008),

Judy Poppell (1969-1973),

Debbie Watson (1969-1973)

North Florida Christian H...

view sourceGraduates:

Michel Foshee (1991-1995),

Elaine Cresse (1970-1974),

Yen Lee (1988-1992),

Kasey Hurst (1994-1998),

Jennifer Wilson (1992-1996)

Elaine Cresse (1970-1974),

Yen Lee (1988-1992),

Kasey Hurst (1994-1998),

Jennifer Wilson (1992-1996)

Sudbury High School, Sudb...

view sourceGraduates:

Ronald Lapchinski (1959-1963),

Yen Lee (1967-1971),

Gerald Sigouin (1947-1951),

Fred MacWilliam (1953-1957),

Luke Luukkonen (1961-1965)

Yen Lee (1967-1971),

Gerald Sigouin (1947-1951),

Fred MacWilliam (1953-1957),

Luke Luukkonen (1961-1965)

St. Ignatius High School,...

view sourceGraduates:

Martin Fu (1993-1996),

Chih Chieh Tsao (1990-1994),

Jerri Hsing (1968-1972),

Yen Lun Lee (1984-1986),

Hsin Hung Lin (1987-1990)

Chih Chieh Tsao (1990-1994),

Jerri Hsing (1968-1972),

Yen Lun Lee (1984-1986),

Hsin Hung Lin (1987-1990)

Youtube

Flickr

Plaxo

Lee Chee Yen

view sourceShah Alam, S'gor, MalaysiaOEM electrical home applainces importer

Yen Lee

view source

Yen Lan Lee

view sourcePortal Manager at Avaya Inc

Oh Lee Yen

view sourceSenior Internal Auditor at CPF Board

Get Report for Yen H Lee from San Francisco, CA, age ~53