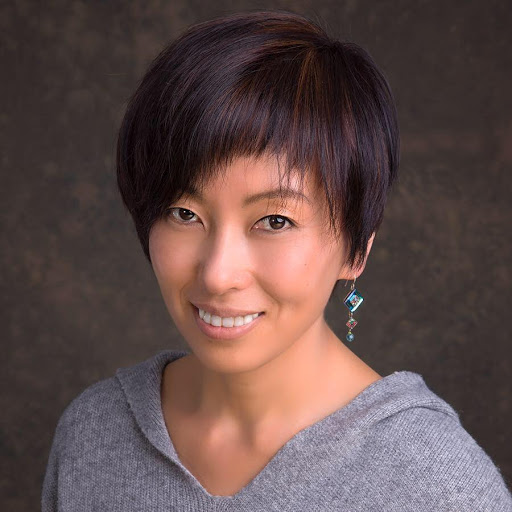

Hong Li Jiang

age ~56

from Arlington, TX

- Also known as:

-

- Hong Liang

- Hong Li Xiang

- Xiang Hong Li

- Xianghong Li

Hong Jiang Phones & Addresses

- Arlington, TX

- 804 Gehring Dr, Kernersville, NC 27284

- Coconut Creek, FL

- Boca Raton, FL

- Irving, TX

- Lauderhill, FL

- Richardson, TX

- Guilford, NC

- Fuquay Varina, NC

Education

-

Degree:Associate degree or higher

Emails

Isbn (Books And Publications)

Small Well Lane: A Contemporary Chinese Play and Oral History

view sourceAuthor

Hong Jiang

ISBN #

0472067958

Small Well Lane: A Contemporary Chinese Play and Oral History

view sourceAuthor

Hong Jiang

ISBN #

0472097954

Fifth International Symposium on Intrumentation and Control Technology

view sourceAuthor

Hong Jiang

ISBN #

0819451371

License Records

Hong Q Jiang

Address:

7875 Glades Rd, Boca Raton, FL 33434

Phone:

(561)4884040

License #:

SEA6020534 - Active

Category:

Restaurants

Renew Date:

Apr 24, 2017

Expiration Date:

Dec 1, 2017

Type:

Permanent Food Service

Organization:

BOCA SHINJU INC

Us Patents

-

Single Ended Preamplifier Having Multiple First Stage Banks For Improved Noise Characteristics

view source -

US Patent:6538832, Mar 25, 2003

-

Filed:Jun 7, 2000

-

Appl. No.:09/589429

-

Inventors:Indumini W. Ranmuthu - Plano TX

Hong Jiang - Plano TX -

Assignee:Texas Instruments Incorporated - Dallas TX

-

International Classification:G11B 509

-

US Classification:360 46, 360 67, 360 63

-

Abstract:In hard disk drives (HDD), a magnetic read head moves over a portion of the hard disk when reading data. A preamplifier, having an initial amplification stage of the single ended type, connects to the magnetic read head and amplifies a data signal picked up by the magnetic read head. The preamplifier typically has multiple read heads, or channels. In order to reduce noise coming into the read channels of the preamplifier from the substrate capacitances of the input transistors connected to the read heads, the input transistors are grouped together into multiple banks that are multiplexed, or turn on separately. To further aid noise reduction, the poles of the single ended amplifier are matched, that is, the frequency response of the constant voltage side is matched to the frequency response to the signal side. This effectively reduces both ground noise and Vcc power supply noise as the the noise becomes common mode on the inputs to a differential amplifier that is connected to the single ended amplifier. Noise is further minimized by connecting the substrates of the switching transistors connected to the input transistors to magnetic read ground, as opposed to integrated circuit ground.

-

Write-To-Read Switching Improvement For Differential Preamplifier Circuits In Hard Disk Drive Systems

view source -

US Patent:6621649, Sep 16, 2003

-

Filed:Nov 10, 2000

-

Appl. No.:09/709699

-

Inventors:Hong Jiang - Plano TX

Indumini Ranmuthu - Plano TX -

Assignee:Texas Instruments Incorporated - Dallas TX

-

International Classification:G11B 502

-

US Classification:360 67, 360 46

-

Abstract:The present invention relates to a preamplifier circuit comprising a plurality of amplifier stages coupled together and operable to consecutively amplify a signal associated with a head of a hard disk drive. The preamplifier circuit further comprises a power delivery circuit operably coupled to the amplifier stages and operable to provide power to the amplifier stages in a substantially concurrent manner when the hard disk drive is transitioning from a write state to a read state. In addition, the circuit comprises a control circuit operably coupled to the amplifier stages, and operable to activate at least two of the plurality of amplifier stages in a generally consecutive manner after the providing of power to the amplifier stages. In the above manner a saturation of an output of the preamplifier circuit is avoided by preventing substantially a propagation of glitches through the preamplifier circuit and providing for a substantially fast write-to-read transition time.

-

Write Head Fault Detection Circuit And Method

view source -

US Patent:6687064, Feb 3, 2004

-

Filed:Jul 21, 2000

-

Appl. No.:09/621107

-

Inventors:Hong Jiang - Plano TX

Paul Merle Emerson - Murphy TX -

Assignee:Texas Instruments Incorporated - Dallas TX

-

International Classification:G11B 509

-

US Classification:360 31, 360 68, 360 46, 369 5342, 340652

-

Abstract:A circuit ( ) and method for detecting faults of a write head ( ) of a hard-disk drive system ( ). A first resistor R and a second resistor R are coupled to coil L of write head ( ). A transistor Q is coupled to a common node of resistor R and R. Current I is applied to the coil L, and voltages V and V across the nodes at either end of resistors R and R are analyzed in order to detect faults on write head coil L. The detection is performed during a quiet mode of the hard-disk drive system ( ), so the fault detection is frequency-independent. Open faults are distinguishable from short-to-ground faults by the write fault detection circuit ( ).

-

Digital Temperature Monitor

view source -

US Patent:6707629, Mar 16, 2004

-

Filed:Jun 30, 2000

-

Appl. No.:09/608896

-

Inventors:Hong Jiang - Plano TX

Paul Merle Emerson - Murphy TX

Bryan E. Bloodworth - Irving TX -

Assignee:Texas Instruments Incorporated - Dallas TX

-

International Classification:G11B 509

-

US Classification:360 67, 360 68

-

Abstract:A digital temperature monitor (DTM ( ) includes a proportional-to-absolute temperature (PTAT) sensor ( ) and reference circuit ( ) coupled to the inputs of a comparator ( ). The DTM ( ) monitors the temperature of adjacent and/or proximate integrated circuitry. The method includes the steps of providing a reference signal to the comparator ( ), increasing the reference signal voltage, and determining the temperature of an integrated circuit by determining when the reference signal is greater than the PTAT sensor ( ) output voltage. The DTM ( ) may be implemented as part of a hard-disk drive preamplifier circuit ( ).

-

Single Pole Voltage Bias Loop For Increased Stability

view source -

US Patent:6724556, Apr 20, 2004

-

Filed:Jun 29, 2001

-

Appl. No.:09/896387

-

Inventors:Indumini W. Ranmuthu - Plano TX

Hong Jiang - Santa Clara CA -

Assignee:Texas Instruments Incorporated - Dallas TX

-

International Classification:G11B 503

-

US Classification:360 66, 360 67, 360 46

-

Abstract:A differential circuit to read differential data from a disk by a voltage bias includes a read circuit having a read circuit pole to read the differential data from the disk by maintaining the voltage bias and a feedback circuit having a feedback pole to sense deviations in the voltage and to adjust the voltage in response to the deviations. The read circuit pole is separated from the feedback pole in frequency.

-

Ca Power Measurement

view source -

US Patent:20200028597, Jan 23, 2020

-

Filed:Dec 31, 2018

-

Appl. No.:16/237578

-

Inventors:- Plano TX, US

Hong Jiang - Kernersville NC, US -

Assignee:Futurewei Technologies, Inc. - Plano TX

-

International Classification:H04B 17/10

H04B 1/40 -

Abstract:A system and method for transmitting and for detecting a transmission power level of a carrier of aggregated carrier signals is configured to generate a plurality of carrier signals as a carrier aggregated signal and to generate an outgoing radio frequency (RF) signal based on the carrier aggregated signal and to produce a feedback signal based the outgoing RF signal. The system process the feedback signal by down converting a first carrier signal within the feedback signal from RF, canceling a down converted harmonically-related signal or an ADC Fs related signal of a second carrier of the carrier aggregated signal and producing a signal representative of the output power of the first carrier of the carrier aggregated signal within the feedback signal.

-

Measurement Receiver Harmonic Distortion Cancellation

view source -

US Patent:20170230067, Aug 10, 2017

-

Filed:Feb 5, 2016

-

Appl. No.:15/016909

-

Inventors:- Plano TX, US

Hong Jiang - Kernersville NC, US -

International Classification:H04B 1/04

H04W 24/08 -

Abstract:A transmitter includes a power amplifier coupled to amplify an input signal and provide an output signal. A radio frequency coupler is coupled to receive the output signal and provide a measured signal on a coupler output. A measurement receiver multiplexor is coupled to receive the measured signal on the coupler output to produce either a non-phase adjusted signal or a phase adjusted signal on one of a plurality of multiplexor outputs. Multiple receiver paths are coupled to the plurality of multiplexor outputs to receive either the non-phase adjusted signal or the phase adjusted signal. Receive path processing circuitry is configured to produce in-phase and quadrature phase digital signals based on the plurality of multiplexor outputs to digital processing circuitry to cancel 3or 3and 5order measurement receiver distortions.

-

System And Method For Clock Spur Artifact Correction

view source -

US Patent:20170111191, Apr 20, 2017

-

Filed:Oct 15, 2015

-

Appl. No.:14/884578

-

Inventors:- Plano TX, US

Hong Jiang - Kernersville NC, US -

International Classification:H04L 25/06

-

Abstract:A method for clock spur artifact correction includes obtaining a plurality of switching stage input signals generated in accordance with an input signal level of an external amplifier, and adjusting the plurality of switching stage input signals such that a clock spur harmonic artifact is reduced. The clock spur harmonic artifact includes a first clock spur harmonic artifact generated in a plurality of external signal paths including external switching stages, and the adjusting the plurality of switching stage input signals includes one of: adjusting a duty ratio of one of the plurality of switching stage input signals in accordance with a gain mismatch between two of the external signal paths; and injecting a first Continuous Wave (CW) signal into the plurality of switching stage input signals in accordance with a previous amplitude of the first clock spur harmonic artifact.

Medicine Doctors

Hong Jiang

view sourceSpecialties:

Neurology

Work:

University Of Miami Medical GroupUniversity Of Miami Neurology

1150 NW 14 St STE 609, Miami, FL 33136

(305)2436732 (phone), (305)2437081 (fax)

1150 NW 14 St STE 609, Miami, FL 33136

(305)2436732 (phone), (305)2437081 (fax)

Languages:

English

Spanish

Spanish

Description:

Dr. Jiang works in Miami, FL and specializes in Neurology. Dr. Jiang is affiliated with Jackson Memorial Hospital and University Of Miami Hospital.

Hong Jiang

view sourceSpecialties:

Pathology

Anatomic Pathology & Clinical Pathology

Dermatopathology

Dermatology

Dermatopathology

Pediatric Otolaryngology

Anatomic Pathology & Clinical Pathology

Dermatopathology

Dermatology

Dermatopathology

Pediatric Otolaryngology

Education:

Xi'An Medical University (1986)

Name / Title

Company / Classification

Phones & Addresses

President

Boca Shinju, Inc

7875 Glades Rd, Boca Raton, FL 33434

President, Director

Shinju Boca, Inc

Business Services at Non-Commercial Site · Nonclassifiable Establishments

Business Services at Non-Commercial Site · Nonclassifiable Establishments

7875 Glades Rd, Boca Raton, FL 33434

16999 SW 16 St, Hollywood, FL 33027

16999 SW 16 St, Hollywood, FL 33027

Director

AMFUTURE SOLUTIONS, INC

Business Services · Nonclassifiable Establishments

Business Services · Nonclassifiable Establishments

4250 Glenhurst Ln, Frisco, TX 75033

2212 Homestead Ln, Plano, TX 75025

2212 Homestead Ln, Plano, TX 75025

Director

ALGOCRAFTS, INC

Computer Related Services

Computer Related Services

116 Keystone Dr, Southlake, TX 76092

2557 Hall Johnson Rd, Grapevine, TX 76051

(682)5036737

2557 Hall Johnson Rd, Grapevine, TX 76051

(682)5036737

President

Asian Market Anaheim Inc

700 S Rosemary Ave, West Palm Beach, FL 33401

7875 Glades Rd, Boca Raton, FL 33434

7875 Glades Rd, Boca Raton, FL 33434

President

Hong Qing Inc

Nonclassifiable Establishments

Nonclassifiable Establishments

17155 Miramar Pkwy, Hollywood, FL 33027

Director, President

David Adams Investments, Incorporated

7777 Glades Rd, Boca Raton, FL 33434

Director

Florida Fujianese Association of America Inc

9200 Belvedere Rd, West Palm Beach, FL 33411

Myspace

Googleplus

Hong Jiang

Work:

Cisco Systems, Inc. - Software Engineer (2001)

Education:

University of California, Santa Cruz - Computer Engineering, Tsinghua University - Computer Science & Engineering

Hong Jiang

Work:

Institute for Simulation and Training

Education:

UCF

Hong Jiang

Hong Jiang

Hong Jiang

Relationship:

Single

Tagline:

MAKE PEACE WITH YOUR PAST SO IT WON'T SPOIL THE PRESENT

Hong Jiang

About:

I hope I can be a good teacher, excellent scholar, sweet wife and cheerful mom. I see needs, I have ideas, but lack of time. I'm a little one who needs God's wisdom and power.

Hong Jiang

Hong Jiang

Flickr

Plaxo

Hong Jiang

view sourceOttawa, OntarioBell Canada

Hong Jiang

view sourceBeijing

Hong Jiang

view sourcesoftware engineer at Cisco Systems

Classmates

Hong Jiang

view sourceSchools:

Fresh Meadows High School Flushing NY 1997-2001

Community:

Stanley Koubek

Hong Jiang

view sourceSchools:

U.C.S.C. Santa Cruz CA 1997-2001

Community:

Audrey Anderson, Victoria Morgan

Fresh Meadows High School...

view sourceGraduates:

Caroline York (1972-1976),

Dorothy Simon (1950-1954),

Barbara van Pelt (1966-1970),

Paul Green (1983-1987),

Hong Jiang (1997-2001)

Dorothy Simon (1950-1954),

Barbara van Pelt (1966-1970),

Paul Green (1983-1987),

Hong Jiang (1997-2001)

U.C.S.C., Santa cruz, Cal...

view sourceGraduates:

Hong Jiang (1997-2001),

Pauline Chow (1998-2002),

Adam Many (1988-1992),

David Keegan (1995-1999),

Tye de Pena (1982-1986),

Lucas Ewell (1997-2001)

Pauline Chow (1998-2002),

Adam Many (1988-1992),

David Keegan (1995-1999),

Tye de Pena (1982-1986),

Lucas Ewell (1997-2001)

Youtube

Hong Jiang

view source

Hong Jiang

view source

Hong Jiang

view source

Hong Jiang

view source

Hong Jiang

view source

Hong Jiang

view source

Hong Jiang

view source

Hong Jiang

view sourceNews

Defying Genetics: How One Patient's Unique Mutation Offers New Hopes in Alzheimer's Prevention

view source- Reference: APOE3ch alters microglial response and suppresses A-induced tau seeding and spread by Yun Chen, Sihui Song, Samira Parhizkar, Jennifer Lord, Yiyang Zhu, Michael R. Strickland, Chanung Wang, Jiyu Park, G. Travis Tabor, Hong Jiang, Kevin Li, Albert A. Davis, Carla M. Yuede, Marco Colonna

- Date: Dec 25, 2023

- Category: Health

- Source: Google

How Intel's Haswell Is More Powerful, But Uses Less Power

view source- Intel senior fellow Tom Piazza joined Intel fellows Hong Jiang and Per Hammarlund, and senior principal engineer Ronak Singhal in a Technology Insight session to provide a detailed examination of the new 22nm technology, which is expected to replace Intel's current third-generation Core ("Ivy Bridge

- Date: Sep 11, 2012

- Category: Sci/Tech

- Source: Google

Get Report for Hong Li Jiang from Arlington, TX, age ~56