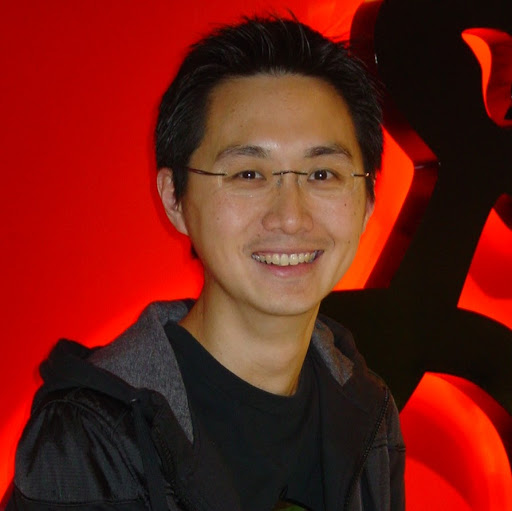

Raymond King Leung

age ~57

from San Jose, CA

- Also known as:

-

- Raymond K Leung

- Raymond King Wai Leung

- Raymond Wai Keung Leung

- Raymond Wai Leung

- Ray King Leung

- Ray K Leung

- Ray Lueng

- Ray Leung King

- Raymond King

- Phone and address:

- 2125 Saffarian Ct, San Jose, CA 95121

Raymond Leung Phones & Addresses

- 2125 Saffarian Ct, San Jose, CA 95121

- 3554 Jasmine Cir, San Jose, CA 95135

- 2956 Lovewood Way, San Jose, CA 95148 • (408)2382882

- 2020 Tradan Dr, San Jose, CA 95132 • (408)2382882

- Phoenix, AZ

- 3137 Pleitner Ave, Oakland, CA 94602

- 3760 Fruitvale Ave, Oakland, CA 94602

- Stockton, CA

- Sharpsburg, MD

- Maricopa, AZ

Medicine Doctors

Raymond K. Leung

view sourceSpecialties:

Pediatrics

Work:

Meadville Pediatrics

765 Liberty St STE 111, Meadville, PA 16335

(814)3366384 (phone), (814)7242771 (fax)

765 Liberty St STE 111, Meadville, PA 16335

(814)3366384 (phone), (814)7242771 (fax)

Education:

Medical School

Univ of Hong Kong, Fac of Med, Hong Kong

Graduated: 1982

Univ of Hong Kong, Fac of Med, Hong Kong

Graduated: 1982

Procedures:

Circumcision

Lumbar Puncture

Destruction of Benign/Premalignant Skin Lesions

Hearing Evaluation

Psychological and Neuropsychological Tests

Vaccine Administration

Lumbar Puncture

Destruction of Benign/Premalignant Skin Lesions

Hearing Evaluation

Psychological and Neuropsychological Tests

Vaccine Administration

Conditions:

Abdominal Hernia

Acute Bronchitis

Acute Conjunctivitis

Acute Otitis Externa

Acute Pharyngitis

Acute Bronchitis

Acute Conjunctivitis

Acute Otitis Externa

Acute Pharyngitis

Languages:

English

Description:

Dr. Leung graduated from the Univ of Hong Kong, Fac of Med, Hong Kong in 1982. He works in Meadville, PA and specializes in Pediatrics. Dr. Leung is affiliated with Meadville Medical Center.

Raymond W. Leung

view sourceSpecialties:

General Surgery, Orthopaedic Surgery

Work:

Healthpointe Medical Group

1717 E Lincoln Ave, Anaheim, CA 92805

(714)6352642 (phone), (714)6358547 (fax)

Healthpointe Medical Group

2226 Medical Ctr Dr STE 101, Perris, CA 92571

(951)6571400 (phone), (951)6570661 (fax)

Raymond W Leung MD

11760 Central Ave STE 204, Chino, CA 91710

(626)5728412 (phone), (626)6983355 (fax)

1717 E Lincoln Ave, Anaheim, CA 92805

(714)6352642 (phone), (714)6358547 (fax)

Healthpointe Medical Group

2226 Medical Ctr Dr STE 101, Perris, CA 92571

(951)6571400 (phone), (951)6570661 (fax)

Raymond W Leung MD

11760 Central Ave STE 204, Chino, CA 91710

(626)5728412 (phone), (626)6983355 (fax)

Education:

Medical School

University of California, San Francisco School of Medicine

Graduated: 1981

University of California, San Francisco School of Medicine

Graduated: 1981

Conditions:

Varicose Veins

Abdominal Hernia

Appendicitis

Breast Disorders

Cholelethiasis or Cholecystitis

Abdominal Hernia

Appendicitis

Breast Disorders

Cholelethiasis or Cholecystitis

Languages:

English

Spanish

Spanish

Description:

Dr. Leung graduated from the University of California, San Francisco School of Medicine in 1981. He works in Perris, CA and 2 other locations and specializes in General Surgery and Orthopaedic Surgery. Dr. Leung is affiliated with Anaheim Regional Medical Center and Gardens Regional Hospital & Medical Center.

Raymond Li-Ming Leung

view sourceSpecialties:

Internal Medicine

Education:

University of Illinois at Chicago (1995)

Us Patents

-

Memory Circuit And Method For Multivalued Logic Storage By Process Variations

view source -

US Patent:58674233, Feb 2, 1999

-

Filed:Apr 10, 1997

-

Appl. No.:8/838799

-

Inventors:Ashok Kapoor - Palo Alto CA

Alex Owens - Los Gatos CA

Thomas R. Wik - Livermore CA

Raymond T. Leung - Palo Alto CA

V. Swamy Irrinki - Milpitas CA -

Assignee:LSI Logic Corporation - Milpitas CA

-

International Classification:G11C 1156

-

US Classification:365168

-

Abstract:A circuit and method which enables storage of more than two logic states in a memory cell by selectively setting threshold voltages of transistors in a memory array according to the present invention. In one embodiment, a memory circuit includes an array of storage transistors. Each storage transistor has a gate connected to an associated read line. When a read line is asserted, the current which flows through a selected storage transistor is indicative of the stored logic state. The current through each transistor is individually selected by setting the threshold voltage of each storage transistor during manufacture. Different transistors in the array are configured with differing threshold voltages to thereby represent different storage states. An analog-to-digital (A/D) converter is coupled to the selected storage transistor so as to sense the current and determine the state represented. Since each cell may represent one of more than two storage states, the memory circuit may advantageously allow an increased number of bits to be stored in each memory cell, thereby increasing the storage density and reducing the cost per bit.

-

Memory System Including An On-Chip Temperature Sensor For Regulating The Refresh Rate Of A Dram Array

view source -

US Patent:57843287, Jul 21, 1998

-

Filed:Dec 23, 1996

-

Appl. No.:8/779999

-

Inventors:V. Swamy Irrinki - Milpitas CA

Ashok Kapoor - Palo Alto CA

Raymond Leung - Palo Alto CA

Alex Owens - Los Gatos CA

Thomas R. Wik - Livermore CA -

Assignee:LSI Logic Corporation - Milpitas CA

-

International Classification:G11C 700

-

US Classification:365222

-

Abstract:A DRAM memory array including a temperature sensor for adjusting a refresh rate depending upon temperature. The DRAM memory array includes a plurality of memory cells, each configured to allow storage and retrieval of more than two discrete memory states. A refresh circuit is coupled to the memory array for periodically refreshing the discrete storage state of each memory cell. The temperature sensor is situated on the same semiconductor die upon which the memory array is fabricated, and generates a signal indicative of the temperature of the semiconductor die. A control circuit receives the signal from the temperature sensor and responsively generates a refresh rate signal which is provided to control the refresh rate of the refresh circuit. In one specific implementation, a ROM look-up table is coupled to the control circuit and includes a plurality of entries which indicate the desired refresh rates for particular temperatures. By controlling the refresh rate dependent upon the temperature of the semiconductor die, proper state retention is ensured within each of the memory cells while allowing performance to be optimized.

-

Memory System Which Enables Storage And Retrieval Of More Than Two States In A Memory Cell

view source -

US Patent:58089322, Sep 15, 1998

-

Filed:Dec 23, 1996

-

Appl. No.:8/779991

-

Inventors:V. Swamy Irrinki - Milpitas CA

Ashok Kapoor - Palo Alto CA

Raymond T. Leung - Palo Alto CA

Alex Owens - Los Gatos CA

Thomas R. Wik - Livermore CA -

Assignee:LSI Logic Corporation - Milpitas CA

-

International Classification:G11C 1124

G11C 1156 -

US Classification:365150

-

Abstract:A memory circuit which enables storage of more than two logic states in a memory cell. Since the additional logic states may be used to represent additional information bits, this memory circuit increases the number of bits that may be stored per memory cell, thereby increasing the storage density and reducing the cost per bit. The disclosed memory circuit comprises an analog-to-digital converter coupled to detect a current through a transistor in a memory cell. The current is determined by a charge stored on the transistor's gate. By enabling the current to be detected in discrete increments, it becomes possible to represent more than one bit of information with the charge stored in the memory cell. Usage of additional increments necessitates more precise storage and detection circuitry. In one embodiment, the storage circuitry uses feedback to obtain a greater logic state retrieval accuracy.

-

Low Power Programming Circuit For User Programmable Digital Logic Array

view source -

US Patent:50457268, Sep 3, 1991

-

Filed:May 16, 1990

-

Appl. No.:7/524329

-

Inventors:Raymond T. Leung - Palo Alto CA

-

Assignee:North American Philips Corporation - Tarrytown NY

-

International Classification:H03K 1712

-

US Classification:307466

-

Abstract:A programming circuit for an array of bipolar transistors which is selectable by row and column decoders to form a selected logic circuit, programming being effected by thermal links respectively connected to the respective transistors and which undergo a change in conductive state when subjected to a programming current of sufficient magnitude. The programming circuit includes a row driver having an FET gate which in response to a row address selection pulse turns on a bipolar transistor (Q1), the FET gate otherwise maintaining Q1 off. Transistor Q1 forms a Darlington pair with any of the transistors in the corresponding row of the array which are turned on. The transistors in respective columns of the array are connected in common by respective column conductors to respective transmission gates, each transmission gate including another Darlington bipolar pair driven by a CMOS inverter. The inverter opens the transmission gate in response to a strobe pulse which is concurrent with a column selection pulse from the column decoder, but otherwise maintains the transmission gate closed. A significant reduction in power consumption, and consequent heat dissipation, is achieved because the row drivers and transmission gates for non-selected rows and columns do not require quiescent operating current, and programming current for a selected transistor is supplied in a path comprising only bipolar Darlington pairs.

-

Memory Cell Capable Of Storing More Than Two Logic States By Using Different Via Resistances

view source -

US Patent:59826592, Nov 9, 1999

-

Filed:Dec 23, 1996

-

Appl. No.:8/779998

-

Inventors:V. Swamy Irrinki - Milpitas CA

Thomas R. Wik - Livermore CA

Raymond T. Leung - Palo Alto CA

Ashok Kapoor - Palo Alto CA

Alex Owens - Los Gatos CA -

Assignee:LSI Logic Corporation - Milpitas CA

-

International Classification:G11C 1156

-

US Classification:365168

-

Abstract:A process which enables storage of more than two logic states in a memory cell. In one embodiment, a via is used to couple a diode between a word read line and a data read line. The via has a resistance which is set to one of a plurality of values at the time of manufacture. When the word read line is asserted, the voltage drop sustained across the via is indicative of the stored logic state. An analog-to-digital (A/D) converter is coupled to the data read line so as to sense the voltage drop and determine the state represented. Since the additional logic states may be used to represent additional information bits, this memory circuit increases the number of bits that may be stored per memory cell, thereby increasing the storage density and reducing the cost per bit.

-

Memory Cell Capable Of Storing More Than Two Logic States By Using Programmable Resistances

view source -

US Patent:57611106, Jun 2, 1998

-

Filed:Dec 23, 1996

-

Appl. No.:8/779992

-

Inventors:V. Swamy Irrinki - Milpitas CA

Ashok Kapoor - Palo Alto CA

Raymond T. Leung - Palo Alto CA

Alex Owens - Los Gatos CA

Thomas R. Wik - Livermore CA -

Assignee:LSI Logic Corporation - Milpitas CA

-

International Classification:G11C 1714

-

US Classification:365100

-

Abstract:A system and process which enables storage of more than two logic states in a memory cell. In one embodiment, a programmable resistor is coupled in series with a transistor between a supply voltage and a data read line. When an access signal is asserted, the transistor provides a conductive path, and a voltage drop is sustained by the programmable resistor. The programmable resistor has a resistance which is set during a programming step to one of a plurality of values by passing a heating current through the programmable resistor for one of a corresponding plurality of predetermined lengths of time. When the access signal is asserted, the voltage drop sustained across the programmable resistor is indicative of the stored logic state. An analog-to-digital (A/D) converter is coupled to the data read line so as to sense the voltage drop and determine the state represented. Since the additional logic states may be used to represent additional information bits, this memory circuit increases the number of bits that may be stored per memory cell, thereby increasing the storage density and reducing the cost per bit.

-

Ram Cell Capable Of Storing 3 Logic States

view source -

US Patent:58479902, Dec 8, 1998

-

Filed:Dec 23, 1996

-

Appl. No.:8/779993

-

Inventors:V. Swamy Irrinki - Milpitas CA

Ashok Kapoor - Palo Alto CA

Raymond T. Leung - Palo Alto CA

Alex Owens - Los Gatos CA

Thomas R. Wik - Livermore CA -

Assignee:LSI Logic Corporation - Milpitas CA

-

International Classification:G11C 1100

-

US Classification:365154

-

Abstract:A memory circuit which enables storage of three logic states in a memory cell. Since the additional logic states may be used to represent additional information bits, this memory circuit increases the number of bits that may be stored per memory cell, thereby increasing the storage density and reducing the cost per bit. The disclosed memory circuit comprises an analog-to-digital converter coupled to detect a current through a transistor in a memory cell. The current is determined by the state of a tri-state flip-flop. By enabling the current to be detected as positive, negative, or zero, it becomes possible to represent more than one bit of information with the state of the flip-flop.

-

Evaluation Of Thermal Instability Stress Testing

view source -

US Patent:20150369855, Dec 24, 2015

-

Filed:Jun 23, 2015

-

Appl. No.:14/748228

-

Inventors:- Mountain View CA, US

Thu Nguyen - Palo Alto CA, US

Shih-Yao Christine Sun - San Jose CA, US

Raymond Tak-Hoi Leung - Palo Alto CA, US -

Assignee:SYNOPSYS, INC. - Mountain View CA

-

International Classification:G01R 31/26

G06F 17/50 -

Abstract:A circuit is powered through a transistor whose thermal instability behavior is to be evaluated in a stress test. The transistor is stressed during a stress phase of the stress test with a sensor circuit powered off and the Vds of the transistor is zero. The sensor circuit is powered on through the transistor during an evaluate phase of the stress test.

Name / Title

Company / Classification

Phones & Addresses

Owner

The Printing Pad Inc

Printers

Printers

1 - 1320 Ellesmere Rd, Scarborough, ON M1P 2X9

(416)3215267

(416)3215267

President

Able Dental Lab Ltd

Dentists-General Practice

Dentists-General Practice

4228 Main St, Vancouver, BC V5V 3P9

(604)8725288

(604)8725288

Owner

Green Earth Engineering-Constr

Management Services

Management Services

968 Hanson Ct, Milpitas, CA 95035

Website: geechome.com

Website: geechome.com

President

Leung, Wong and Choi Inc

Accounting/Auditing/Bookkeeping

Accounting/Auditing/Bookkeeping

8 California St, San Francisco, CA 94111

Owner

The Printing Pad Inc

Printers

Printers

(416)3215267

President

Able Dental Lab Ltd

Dentists-General Practice

Dentists-General Practice

(604)8725288

President

ASM INSURANCE AND FINANCIAL SERVICES, INC

2001 Junipero Serra Blvd SUITE 550, Daly City, CA 94014

270 Morningside Dr, San Francisco, CA 94132

270 Morningside Dr, San Francisco, CA 94132

Owner

Green Earth Engineering & Construction

Other Heavy Construction

Other Heavy Construction

968 Hanson Ct, Milpitas, CA 95035

(408)2632188

(408)2632188

Lawyers & Attorneys

Raymond Jack Leung, Oakland CA - Lawyer

view sourceAddress:

ChangeLab Solutions

2201 Broadway Ste 502, Oakland, CA 94612

2201 Broadway Ste 502, Oakland, CA 94612

Licenses:

California - Active 2007

Education:

New York University School of Law

University of California - Berkeley

University of California - Berkeley

Resumes

Process Engineer At Xradia, Inc.

view sourcePosition:

Process Engineer at Xradia, Inc.

Location:

San Francisco Bay Area

Industry:

Nanotechnology

Work:

Xradia, Inc. - Pleasanton, CA since Sep 2011

Process Engineer

Xradia, Inc. - Pleasanton, CA Jan 2011 - Sep 2011

Research & Development Intern

Caltrans Jun 2007 - Aug 2008

Transportation Engineer Assistant

Process Engineer

Xradia, Inc. - Pleasanton, CA Jan 2011 - Sep 2011

Research & Development Intern

Caltrans Jun 2007 - Aug 2008

Transportation Engineer Assistant

Education:

University of California, Davis 2009 - 2010

M.S., Civil Engineering University of California, Berkeley 2005 - 2009

B.S., Civil Engineering

M.S., Civil Engineering University of California, Berkeley 2005 - 2009

B.S., Civil Engineering

Skills:

Product Development

Data Analysis

Optics

X-ray

Matlab

Microsoft Excel

JMP

Engineering Statistics

MEMS

Thin Films

SPC

Solidworks

Image Processing

ImageJ

Design of Experiments

Materials Science

Data Analysis

Optics

X-ray

Matlab

Microsoft Excel

JMP

Engineering Statistics

MEMS

Thin Films

SPC

Solidworks

Image Processing

ImageJ

Design of Experiments

Materials Science

Interests:

Digital Photography

Awards:

Award for Excellence

Vice President of Engineering, Xradia

Identification of the opportunity, development of an innovative solution and qualification of a method to reduce the cycle time for capillary x-ray condensers by more than a factor of two

Vice President of Engineering, Xradia

Identification of the opportunity, development of an innovative solution and qualification of a method to reduce the cycle time for capillary x-ray condensers by more than a factor of two

Certifications:

EIT, Board for Professional Engineers and Land Surveyors

Exploring New And Exciting Opportunities

view sourceLocation:

San Francisco, California

Industry:

Facilities Services

Work:

Skidmore Owings & Merrill LLP (SOM) Oct 2005 - Dec 2012

Office Services

Prager, Sealy & Co., LLC - San Francisco Bay Area Jul 2000 - Sep 2004

Operations Assistant

Pitney Bowes Management Services - San Francisco Bay Area Oct 1995 - Aug 1997

Production Associate / Team Leader

RR Donnelley - San Francisco Bay Area Jan 1994 - May 1995

Production Lead

SNR Denton - San Francisco Bay Area Apr 1990 - Apr 1993

Office Services

Office Services

Prager, Sealy & Co., LLC - San Francisco Bay Area Jul 2000 - Sep 2004

Operations Assistant

Pitney Bowes Management Services - San Francisco Bay Area Oct 1995 - Aug 1997

Production Associate / Team Leader

RR Donnelley - San Francisco Bay Area Jan 1994 - May 1995

Production Lead

SNR Denton - San Francisco Bay Area Apr 1990 - Apr 1993

Office Services

Development Engineer Newport Corp. Irvine

view sourcePosition:

Development Engineer at Newport Corp.

Location:

Irvine, California

Industry:

Mechanical or Industrial Engineering

Work:

Newport Corp. since 2010

Development Engineer

Williams Furnace Company 2007 - 2010

Mechanical Engineer

Oshkosh Corporation / AK Specialty Vehicle 2000 - 2007

Project Engineer

Amphastar Pharmaceuticals, Inc. - Rancho Cucamonga 1999 - 2000

Mechanical Engineer

Magnecomp - Temecula 1997 - 1999

Program Engineer

Development Engineer

Williams Furnace Company 2007 - 2010

Mechanical Engineer

Oshkosh Corporation / AK Specialty Vehicle 2000 - 2007

Project Engineer

Amphastar Pharmaceuticals, Inc. - Rancho Cucamonga 1999 - 2000

Mechanical Engineer

Magnecomp - Temecula 1997 - 1999

Program Engineer

Education:

Cal Poly Pomona 1994 - 1997

BSME

BSME

Human Resources At Cisco Systems

view sourcePosition:

HR Specialist at Cisco Systems

Location:

San Jose, California

Industry:

Human Resources

Work:

Cisco Systems since Jun 2012

HR Specialist

Cisco Systems May 2011 - Aug 2011

HR Intern, Students To Experienced Professionals (STEP)

Marvell Semiconductor Nov 2010 - Mar 2011

HR Immigration Assistant

City of San Jose Jun 2010 - Nov 2010

Intern, Office of Councilmember Pete Constant - District 1

Saks Fifth Avenue Sep 2009 - Aug 2010

Selling and Service Associate

HR Specialist

Cisco Systems May 2011 - Aug 2011

HR Intern, Students To Experienced Professionals (STEP)

Marvell Semiconductor Nov 2010 - Mar 2011

HR Immigration Assistant

City of San Jose Jun 2010 - Nov 2010

Intern, Office of Councilmember Pete Constant - District 1

Saks Fifth Avenue Sep 2009 - Aug 2010

Selling and Service Associate

Education:

San Jose State University 2008 - 2012

BS, Business Administration, Concentration in Human Resource Management / Minor - Political Science

BS, Business Administration, Concentration in Human Resource Management / Minor - Political Science

Skills:

Human Resources

HRIS

Onboarding

Program Management

Microsoft Office

Compensations

Building Relationships

Stocks

Payroll

Social Networking

Performance Appraisal

HRIS

Onboarding

Program Management

Microsoft Office

Compensations

Building Relationships

Stocks

Payroll

Social Networking

Performance Appraisal

Awards:

Cisco Social Media Specialist Certificate

Cisco Systems

Cisco Systems

Raymond Leung

view sourceLocation:

United States

Raymond Leung

view sourceLocation:

United States

Raymond Leung San Francisco, CA

view sourceWork:

SKIDMORE OWINGS & MERRILL

San Francisco, CA

Oct 2005 to Dec 2012

OFFICE SERVICES CLERK KIRKLAND & ELLIS

San Francisco, CA

Dec 2004 to Aug 2005

OFFICE SERVICES CLERK PRAGER & COMPANY, LLC

San Francisco, CA

Jul 2000 to Sep 2004

Operations Assistant PRUDENTIAL VOLPE TECHNOLOGY GROUP

San Francisco, CA

Sep 1999 to Jun 2000

OFFICE SERVICES ADMINISTRATOR SHEARMAN & STERLING (employed by Pitney Bowes Management Services)

San Francisco, CA

Nov 1997 to Sep 1999

TEAM LEAD / RECORDS SUPERVISOR BARGER & WOLEN

San Francisco, CA

Jan 1997 to Nov 1997

OFFICE SERVICES CLERK STEEFEL LEVITT & WEISS

San Francisco, CA

Aug 1995 to Apr 1996

REPROGRAPHICS TECHNICIAN ORRICK HERRINGTON & SUTCLIFFE (employed by R.R. Donnelley Business Services)

San Francisco, CA

Jan 1994 to May 1995

PRODUCTION ASSOCIATE SONNENSCHEIN NATH & ROSENTHAL

San Francisco, CA

Apr 1990 to Apr 1993

OFFICE SERVICES CLERK

San Francisco, CA

Oct 2005 to Dec 2012

OFFICE SERVICES CLERK KIRKLAND & ELLIS

San Francisco, CA

Dec 2004 to Aug 2005

OFFICE SERVICES CLERK PRAGER & COMPANY, LLC

San Francisco, CA

Jul 2000 to Sep 2004

Operations Assistant PRUDENTIAL VOLPE TECHNOLOGY GROUP

San Francisco, CA

Sep 1999 to Jun 2000

OFFICE SERVICES ADMINISTRATOR SHEARMAN & STERLING (employed by Pitney Bowes Management Services)

San Francisco, CA

Nov 1997 to Sep 1999

TEAM LEAD / RECORDS SUPERVISOR BARGER & WOLEN

San Francisco, CA

Jan 1997 to Nov 1997

OFFICE SERVICES CLERK STEEFEL LEVITT & WEISS

San Francisco, CA

Aug 1995 to Apr 1996

REPROGRAPHICS TECHNICIAN ORRICK HERRINGTON & SUTCLIFFE (employed by R.R. Donnelley Business Services)

San Francisco, CA

Jan 1994 to May 1995

PRODUCTION ASSOCIATE SONNENSCHEIN NATH & ROSENTHAL

San Francisco, CA

Apr 1990 to Apr 1993

OFFICE SERVICES CLERK

Education:

San Francisco State University

San Francisco, CA

2014

Bachelor of Arts in Psychology

San Francisco, CA

2014

Bachelor of Arts in Psychology

Raymond Leung Fremont, CA

view sourceWork:

Walgreen's Pharmacy

Oct 2006 to Present

Senior Certified and Licensed Pharmacy Technician Starbuck's

Hayward, CA

Jun 2005 to Sep 2005

Barista Target

Cupertino, CA

Sep 2004 to Apr 2005

Price Change Staff

Oct 2006 to Present

Senior Certified and Licensed Pharmacy Technician Starbuck's

Hayward, CA

Jun 2005 to Sep 2005

Barista Target

Cupertino, CA

Sep 2004 to Apr 2005

Price Change Staff

Education:

Skyline College

San Bruno, CA

Jan 2008 to Sep 2009

Bachelor in Biology Chabot College

Hayward, CA

Jan 2006 to Dec 2007

Associates in Biology

San Bruno, CA

Jan 2008 to Sep 2009

Bachelor in Biology Chabot College

Hayward, CA

Jan 2006 to Dec 2007

Associates in Biology

Youtube

Googleplus

Raymond Leung

Work:

Raymond WP Leung M.D. Inc - Staff surgeon (1986)

Self employed

Self employed

Education:

UC San Francisco - Medicine

Tagline:

God's faithful servant

Raymond Leung

Work:

National Instruments - Field Sales Engineer (2012)

National Instruments - Applications Engineer (2007-2011)

National Instruments - Applications Engineer (2007-2011)

Education:

University of Auckland - ECE

Raymond Leung

Work:

Raymond & Jessie Leung Photography - Wedding Photojournalist (2005)

Education:

Simon Fraser University - Chemistry

Tagline:

Raymond and Jessie are international award winning wedding photographers. They were named by Weddingbells Magazine as 30 Most Inspiring Photographers for 2011. As a husband-&-wife team, they bring both the male and female perspectives to each wedding they document. The couple captures precious moments as fine art with an innovative photojournalistic approach. Their works go beyond traditional portraiture to present each photo as a storytelling of places and events with people expressing true emotions.

Raymond Leung

Education:

University of Toronto - Religious Studies, Philosophy, Classical Studies, Regent College - Divinity

Raymond Leung

Education:

University of California, Berkeley - Civil & Environmental Engineering, University of California, Davis - M.S. in Civil Transportation Engineering

Raymond Leung

Work:

Cisco Systems, Inc. - Human Resources (2011)

Education:

San Jose State University - Business Administration: HR

Raymond Leung

Work:

Neo@Ogilvy

Education:

Hong Kong Baptist University - Communication

Raymond Leung

Work:

St. Paul's Anglican Bankstown

Education:

Moore Theological College

Plaxo

Raymond Leung

view sourceI refuse to let practical considerations prevent me from achieving my impractical goals. Must they be mutually exclusive? No, practical considerations can serve... I refuse to let practical considerations prevent me from achieving my impractical goals. Must they be mutually exclusive? No, practical considerations can serve the impractical goal.

Raymond Leung

view source

Raymond Leung

view sourceTST, Kowloon, Hong Kong

Myspace

Get Report for Raymond King Leung from San Jose, CA, age ~57

![[HD] Kerry Lynne Findlay, Alice Wong, Ronald Leung... [HD] Kerry Lynne Findlay, Alice Wong, Ronald Leung...](https://i.ytimg.com/vi/JWufakRfk5g/0.jpg)